Агуулгын хүснэгт:

- Зохиолч John Day day@howwhatproduce.com.

- Public 2024-01-30 11:02.

- Хамгийн сүүлд өөрчлөгдсөн 2025-01-23 15:00.

Энэхүү зааварчилгааны хүрээнд бид VHDL дээр эхнээс нь SPI автобусны мастер зохион бүтээх гэж байна.

Алхам 1: SPI -ийн тойм

- SPI бол синхрон цуваа автобус юм

- Түгээмэл тархсан байдал, энгийн байдал нь үүнийг цуврал харилцааны де -факто стандарт болгосон

- Бүрэн дуплекс автобус

- Энгийн протокол ба хамгийн хурдан цуваа автобусны нэг

Алхам 2: Дизайн техникийн үзүүлэлтүүд

Эдгээр нь бидний төлөвлөж буй SPI Master -ийн техникийн үзүүлэлтүүд юм.

- Үйл ажиллагааны бүх дөрвөн горимыг дэмждэг; динамикаар тохируулах боломжтой

- Цаг нь эрчим хүч хэмнэх хяналтыг идэвхжүүлдэг

- Статик тохируулгатай үгийн урт ба хурд

- Дамжуулах болон хүлээн авах аль алинд нь ганц тасалдал

Алхам 3: Эхлэх

Юуны өмнө манай IP хоёр интерфэйстэй байх ёстой. Нэг нь цуваа интерфэйс, нөгөө нь зэрэгцээ интерфэйс юм. Цуваа интерфэйс нь SPI-ийн де-факто стандарт дохионуудаас бүрдэнэ: MOSI, MISO, SS, SCLK.

MOSI -ийг заримдаа SDO, MISO -ийг заримдаа SDI гэж нэрлэдэг.

Цуваа интерфэйс нь гадаад захын төхөөрөмжүүдтэй, өөрөөр хэлбэл SPI боолуудтай харилцахад ашиглагддаг.

Зэрэгцээ интерфейс нь манай хосттой, өөрөөр хэлбэл микроконтроллер эсвэл микропроцессортой харилцахад ашиглагддаг бөгөөд энэ нь дамжуулалтаар ямар өгөгдлийг цуваа дамжуулж, хүлээн авах ёстойг Мастерт үнэнээр нь хэлдэг. өөрөөр хэлбэл, бүх өгөгдлийн автобусууд зэрэгцээ интерфэйсд хамаарна.

Бид дотоод SPI логикийг жолооддог дэлхийн цагтай, мөн дотооддоо үйлдвэрлэдэг SCLK -тэй.

Бидэнд бичих идэвхжүүлэх, цаг идэвхжүүлэх гэх мэт хяналтын дохионууд байдаг. Мөн тасалдал болон бусад статусын дохио.

Хяналтын нарийн төвөгтэй нөхцлүүдийг шийдвэрлэх шаардлагатай байдаг тул ийм цуваа холбооны IP -ийг FSM хэлбэрээр зохион бүтээх нь илүү хялбар байдаг. Бид SPI мастерийг FSM хэлбэрээр зохион бүтээнэ. FSM нь SCLK -ээс хоёр дахин их өөр дотоод цагаар удирдуулах болно. Энэхүү дотоод цагийг дэлхийн цагны синхрон тоолуур ашиглан бүтээдэг.

Цагийн хүрээг хамарсан бүх хяналтын дохио нь аюулгүй талдаа байх синхронизатортой байдаг.

Алхам 4: SPI Master Core ба Simulation Waveforms -ийн RTL харагдац

Энэ бол зориулалтын FPGA IP ашиглаагүй нүцгэн RTL загвар юм. Тиймээс энэ нь аливаа FPGA -д бүрэн зөөврийн код юм.

Зөвлөмж болгож буй:

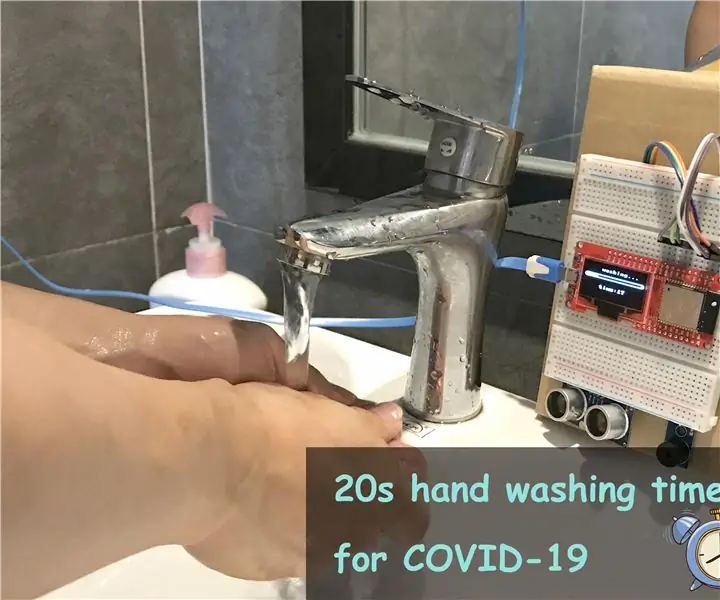

COVID-19-д зориулсан 20 дахь хоёр дахь гар угаах таймер: 6 алхам (зурагтай)

COVID-19-д зориулсан хоёр дахь гар угаах таймер: Дэлхий даяар COVID-19 тархах тусам бид нүүрээ бага багаар цуглуулж, гараа илүү олон удаа угааж өөрийгөө хамгаалах ёстой. гараа зөв угааж болохгүй. Гараа хэрхэн зөв угаах вэ? W

VHDL дээр програмчлагдах тасалдлын хянагчийн дизайн: 4 алхам

VHDL -д програмчлагдах тасалдлын хянагчийн загвар: Энэ блог дээр надад ямар төрлийн хариулт өгч байгаад би сэтгэл дундуур байна. Миний блогоор зочилж, мэдлэгээ та бүхэнтэй хуваалцах урам зориг өгсөн залуусдаа баярлалаа. Энэ удаад би бүх SOC -д харагддаг өөр нэг сонирхолтой модулийн загварыг танилцуулах болно - Interrupt C

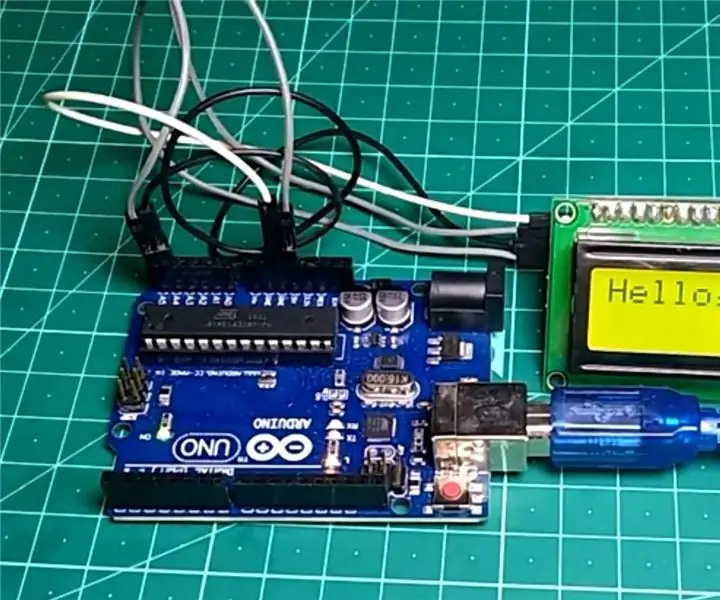

I2C / IIC LCD дэлгэц - Arduino ашиглан SPI -IIC модулийг ашиглан I2C LCD дэлгэц рүү SPI LCD ашиглах: 5 алхам

I2C / IIC LCD дэлгэц | IUC LCD дэлгэц дээр SPI LCD дэлгэцийг SPI -ийг IIC модулийг ашиглан Arduino ашиглан ашиглаарай: Сайн байна уу залуусаа, ердийн SPI LCD 1602 -ийг холбоход хэт олон утас байдаг тул үүнийг arduino -той холбоход маш хэцүү боловч зах зээл дээр боломжтой нэг модуль байдаг. SPI дэлгэцийг IIC дэлгэц болгон хөрвүүлэх тул та зөвхөн 4 утас холбох хэрэгтэй

VHDL дээрх I2C мастер дизайн: 5 алхам

VHDL дээрх I2C мастер дизайн

VHDL ба Verilog дээр энгийн VGA хянагчийн дизайн: 5 алхам

VHDL ба Verilog дээрх энгийн VGA хянагчийн загвар: Энэхүү зааварчилгаанд бид RTL дээр энгийн VGA хянагч зохион бүтээх гэж байна. VGA хянагч нь VGA дэлгэцийг удирдах зориулалттай дижитал хэлхээ юм. Энэ нь харуулах хүрээг харуулсан Frame Buffer (VGA санах ой) -оос уншиж, шаардлагатай зүйлийг үүсгэдэг