Агуулгын хүснэгт:

- Зохиолч John Day day@howwhatproduce.com.

- Public 2024-01-30 11:02.

- Хамгийн сүүлд өөрчлөгдсөн 2025-01-23 15:00.

Би энэ блог дээр ямар төрлийн хариулт өгч байгаад дарагдаж байна. Миний блогоор зочилж, мэдлэгээ та бүхэнтэй хуваалцах урам зориг өгсөн залуусдаа баярлалаа. Энэ удаад би бүх SOC -д харагддаг өөр нэг сонирхолтой модулийн загварыг танилцуулах болно - Interrupt Controller.

Бид энгийн боловч хүчирхэг програмчлагдах тасалдлын хянагч зохион бүтээх болно. Энэ бол платформ даяар зөөврийн байдлаар бүрэн тохируулагдсан, параметртэй дизайн юм. Би үүнийг NVIC, 8259a, RISC-V PLIC, Microblaze-ийн INTC гэх мэт алдартай тасалдлын хянагчийн архитектурыг маш их уншсаны дараа үүнийг зохион бүтээсэн. тасалдлын хянагчийн тусламжтайгаар.

Алхам 1: Техникийн үзүүлэлтүүд

IP -ийн техникийн үзүүлэлтүүдийг энд харуулав.

- AHB3-Lite интерфэйс.

-

Статик тохируулгатай параметрүүд:

- Гаднах тасалдлын эх үүсвэрийн тоо; 63 хүртэлх тасалдлыг дэмждэг.

- Тэргүүлэх түвшний тоо; 63 түвшинг дэмждэг.

- Үүрлэх түвшний тоо; үүрлэх 8 хүртэлх түвшинг дэмждэг.

- Автобусны өргөн; 32 эсвэл 64.

- Дэлхий даяар болон орон нутагт маск хийх боломжтой тасалдал.

- Тасалдал бүрийн хувьд динамикаар тохируулах тэргүүлэх түвшин.

- Үйл ажиллагааны хоёр горим - Бүрэн ороосон горим ба Тэнцүү давуу эрхийн горим.

- Идэвхтэй өндөр түвшний мэдрэмтгий тасалдлыг дэмждэг.

Дизайн хийхэд RISC-V PLIC-ийн тодорхойлолтуудыг өдөөсөн гар барих механизмыг ашигласан болно.

Тасалдлын урьдчилсан шингээлтийг 8259a-аас авсан болно

Бусад уншлага: Microblaze INTC, NVIC

Алхам 2: PIC -ийн тойм

Програмчлагдах тасалдлын хянагч (PIC) нь гадаад захын төхөөрөмжөөс олон тасалдал хүлээн авч, тэдгээрийг нэг тасалдалт гаралт болгон зорилтот процессорын цөмд нэгтгэдэг.

PIC нь хяналт, статусын бүртгэлээр хянагддаг. Бүх PIC регистрүүд нь санах ойн зураглалтай бөгөөд AHB3-Lite автобусны интерфейсээр дамждаг.

Бүртгэлийн банк нь тасалдлын хянагчдад түгээмэл байдаг тохиргооны бүртгэл, идэвхжүүлэх бүртгэл, хүлээгдэж буй бүртгэл, үйлчилгээнд хамрагдах бүртгэл, тэргүүлэх бүртгэл, ID бүртгэлээс бүрдэнэ.

Тохиргооны бүртгэлийг PIC -ийн ажиллах горимыг тохируулахад ашигладаг. Энэ нь бүрэн ороосон горим эсвэл ижил давуу эрхийн горимд ажиллах боломжтой.

Тасалдал болгонд тэргүүлэх ач холбогдол өгч, дангаар нь маск хийж болно. Бүх тасалдлыг дэлхий даяар далдлахыг дэмждэг.

Бүртгэлийн банк нь Priority Resolver болон BTC (Binary-Tree-Comparator) -тай харилцан үйлчлэлцэж байгаа тасалдлын тэргүүлэх чиглэлийг шийдвэрлэж, үүний дагуу процессор тасалдсан гэж мэдэгддэг. ID бүртгэл нь тасалдал хүлээж буй хамгийн чухал ач холбогдолтой ID -г агуулдаг.

Алхам 3: RTL дизайн ба хэрэгжилт

Загварын хамгийн чухал хэсэг болох тэргүүлэх чиглэлийг шийдвэрлэх хоцролтыг багасгахад PIC -ийн дизайны стресс. Энэхүү загвар нь тэргүүлэх чиглэлийг нэг цагийн мөчлөгөөр шийддэг тул Log2 нарийн төвөгтэй эх үүсвэрийн тоо нэмэгдэх тусам гүйцэтгэл буурдаг.

Энэхүү загварыг амжилттай хэрэгжүүлж, Artix-7 FPGA-ийн давтамжийг дагаж мөрдөх хугацааг баталгаажуулав.

- 15 хүртэлх эх үүсвэр: 100 МГц

- 63 эх үүсвэр хүртэл: 50 МГц

Зөвхөн PIC -ийн нэмсэн тасалдлын хоцрогдол нь 3 цагийн мөчлөг юм (Процессорын контекст шилжих хугацаа болон ISR -ийн анхны зааврыг авах хугацааг оруулаагүй болно).

Алхам 4: Чухал тэмдэглэл ба хавсаргасан файлууд

Чухал тэмдэглэл:

- Хэрэв AHB3-Lite интерфэйс нь хүсээгүй бол та дээд модулийг өөрчилж, PIC-ийн араг ясны загварыг ашиглаж болно. Гэсэн хэдий ч туршилтын вандан нь AHB3-Lite интерфэйстэй IP-т зориулагдсан болно.

- PIC IP v1.0 бол бүрэн зөөврийн, нүцгэн RTL загвар юм.

- Хоёр горим дээр ажиллахын тулд функциональ байдлаар баталгаажсан.

Хавсаргасан файлууд:

- VHDL дээрх кодууд ба тестийн ширээ.

- IP -ийн бүрэн баримт бичиг.

Энэ бол нээлттэй эхийн загвар юм … ашиглахад чөлөөтэй…

Ямар ч асуултанд, хүссэн үедээ:

Миту Раж

Зөвлөмж болгож буй:

Тасалдлын лаборатори (Ажил үргэлжилж байна): 3 алхам

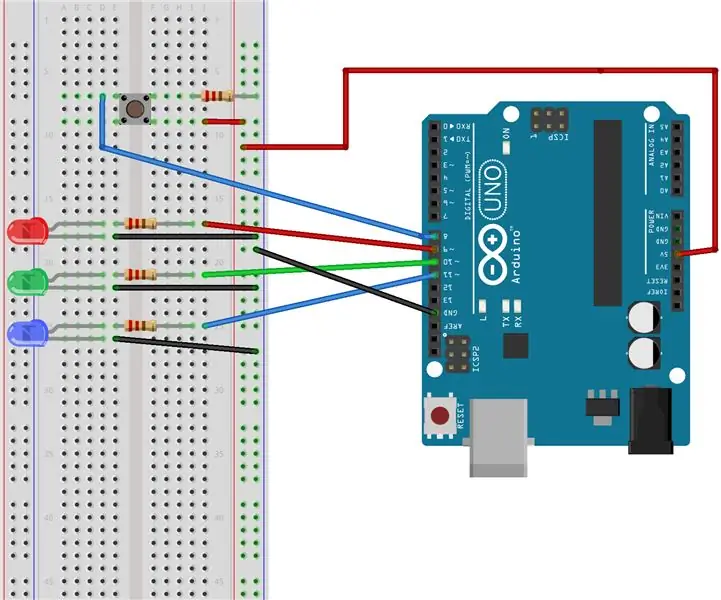

Тасалдалтын лаборатори (Ажил үргэлжилж байна): Энэхүү лабораторийн зорилго нь тасалдал ашиглан Arduino програмыг ажиллуулах явдал юм. Энэ лаборатори нь кодчиллын асуудлаас болж бүрэн ажиллахгүй байгаа бөгөөд танд хэрэгтэй болно:- 1 Arduino Uno- 1 Breadboard- 1 товчлуур- 3 LED- 220 Ом эсэргүүцэл- Холбогч утас

VHDL дээрх дөрвөн талт энгийн ассоциатив кэш хянагчийн загвар: 4 алхам

VHDL дээрх дөрвөн талт энгийн ассоциатив кэш хянагчийн загвар: Миний өмнөх зааварчилгаанд бид энгийн шууд зураглал бүхий кэш хянагчийг хэрхэн яаж бүтээх талаар олж мэдсэн. Энэ удаад бид нэг алхам урагшилж байна. Бид дөрвөн талын энгийн ассоциатив кэш хянагчийн загварыг гаргах болно. Давуу тал? Алдагдсан ханш бага, гэхдээ үнийн хувьд

VHDL дээрх энгийн кэш хянагчийн загвар: 4 алхам

VHDL дээрх энгийн кэш хянагчийн загвар: Би үүнийг зааж өгч байна, учир нь VHDL кодыг сурч, кэш хянагч зохион бүтээхэд жаахан хэцүү байсан. Тиймээс би өөрөө кэш хянагчийг эхнээс нь зохион бүтээсэн бөгөөд үүнийг FPGA дээр амжилттай туршсан. Надад п байна

VHDL ба Verilog дээр энгийн VGA хянагчийн дизайн: 5 алхам

VHDL ба Verilog дээрх энгийн VGA хянагчийн загвар: Энэхүү зааварчилгаанд бид RTL дээр энгийн VGA хянагч зохион бүтээх гэж байна. VGA хянагч нь VGA дэлгэцийг удирдах зориулалттай дижитал хэлхээ юм. Энэ нь харуулах хүрээг харуулсан Frame Buffer (VGA санах ой) -оос уншиж, шаардлагатай зүйлийг үүсгэдэг

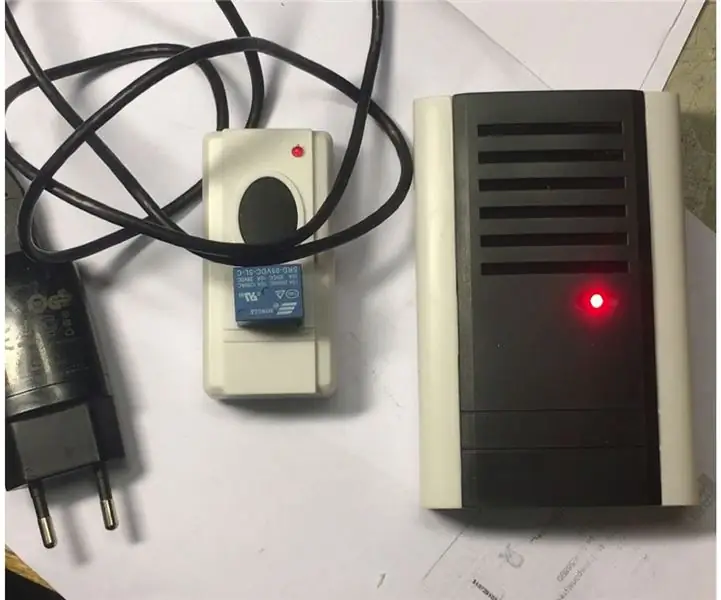

Хөлдөөгчийн цахилгаан тасалдлын дохиолол: 6 алхам (зурагтай)

Хөлдөөгчид зориулсан цахилгаан тасалдлын дохиолол: Хонгилд хөлдөөгчтэй, биднийг хол байх үед гал хамгаалагч нь шатаж, мах нь ялзрах эрсдэлтэй тул би энэхүү энгийн дохиоллын хэлхээг зохион бүтээсэн бөгөөд ингэснээр хөршүүддээ гал хамгаалагчийг засварлахад анхааруулах болно. Зурган дээрээс харахад хаалганы хонх дуугарч байна