Агуулгын хүснэгт:

- Алхам 1: Блок диаграм

- Алхам 2: Үйл ажиллагааны зарчим

- Алхам 3: Логик хэрэгжилт

- Алхам 4: Түгжрэлийг шийдвэрлэх

- Алхам 5: Төхөөрөмжийн тохиргоо - Matrix0 хэлхээ

- Алхам 6: Төхөөрөмжийн тохиргоо - SPI цагны логик

- Алхам 7: Төхөөрөмжийн тохиргоо - Matrix0 бүрэлдэхүүн хэсгүүдийн шинж чанар

- Алхам 8: Төхөөрөмжийн тохиргоо - Matrix1 хэлхээ

- Алхам 9: Төхөөрөмжийн тохиргоо - 3 битийн хоёртын тоолуур

- Алхам 10: Төхөөрөмжийн тохиргоо - 3 битийн харьцуулах логик

- Алхам 11: Төхөөрөмжийн тохиргоо - Дижитал харьцуулах логик ба түр бүртгэл

- Алхам 12: Төхөөрөмжийн тохиргоо - Matrix1 бүрэлдэхүүн хэсгүүдийн шинж чанарууд

- Алхам 13: Үр дүн

- Зохиолч John Day day@howwhatproduce.com.

- Public 2024-01-30 11:01.

- Хамгийн сүүлд өөрчлөгдсөн 2025-01-23 15:00.

Хяналтын системүүд болон холбогдох төхөөрөмжүүд нь хэвийсэн шугам, батерей гэх мэт олон төрлийн тэжээлийн эх үүсвэрүүдтэй ажилладаг бөгөөд тухайн багц дотроос хамгийн өндөр (эсвэл хамгийн бага) шугамыг хянах ёстой.

Жишээлбэл, "олон батерей" -тай системд ачаалал солихын тулд систем нь батерейны массивын хамгийн бага эсвэл хамгийн их хүчдэлийг хянах ёстой (тухайн шилжих алгоритмын функцээр хамгийн их эсвэл хамгийн бага) ба ачааллыг динамикаар чиглүүлдэг. бодит цаг хугацаанд хамгийн тохиромжтой эх сурвалж. Эсвэл зөв цэнэглэхийн тулд систем хамгийн бага хүчдэлийн батерейг түр салгах шаардлагатай болж магадгүй юм.

Өөр нэг жишээ бол орчин үеийн нарны эрчим хүчний систем бөгөөд нарны хавтан бүр нь титротатын механизмаар тоноглогдсон, нарны хянах хэлхээтэй байдаг (сүүлийнх нь хавтанг чиглүүлэх Нарны байрлалын мэдээллийг өгдөг). Хамгийн их хүчдэлийн мэдээллийн тусламжтайгаар нарны хавтангийн байрлал бүрийг хамгийн өндөр гаралтын хүчдэлийг дамжуулж буй утасны хавтангийн үндсэн дээр нарийн тохируулж, улмаар эрчим хүчний оновчлолын дээд түвшинг хангаж өгдөг.

Зарчмын хувьд хамгийн их хүчдэлийн дагалдагчийг хэрэгжүүлэх боломжтой арилжааны IC -ийн хэд хэдэн өөр брэндүүд байдаг (ихэвчлэн микроконтроллерууд). Гэсэн хэдий ч тэдгээр нь програмчлалыг шаарддаг бөгөөд холимог дохионы шийдэлтэй харьцуулахад өртөг багатай байдаг. Dialog GreenPAKTM загварыг нэмж оруулах нь дизайны боломжийн байдал, хэмжээ, модульд эерэгээр нөлөөлнө. Энэхүү загвар нь аналог болон дижитал хэлхээг нэг чип болгон нэгтгэх давуу талыг ашигладаг.

Энэхүү зааварт гарын авлагад найман өөр эх үүсвэрээс хамгийн их (эсвэл эцэст нь мин) хүчдэлийн илрүүлэгчийг хэрэгжүүлэхэд шаардлагатай аналог фронт ба дижитал логикийг хэрэгжүүлсэн болно.

8 сувгийн аналог макс/мин хүчдэлийн дэлгэцийг ашиглахын тулд SLG46620G ашигладаг.

Доор бид 8 сувгийн аналог макс/мин хүчдэлийн мониторыг бий болгохын тулд уг шийдлийг хэрхэн програмчилсан болохыг ойлгох алхмуудыг тайлбарласан болно. Гэсэн хэдий ч хэрэв та програмчлалын үр дүнг авахыг хүсч байвал GreenPAK програмыг татаж аваад аль хэдийн дууссан GreenPAK дизайны файлыг үзнэ үү. GreenPAK Development Kit-ийг компьютер дээрээ залгаж, 8 сувгийн аналог макс/мин хүчдэлийн мониторыг бүтээхийн тулд програмыг дарна уу.

Алхам 1: Блок диаграм

Зураг 1 -т хэрэгжүүлсэн системийн дэлхийн диаграммыг харуулав.

8 хүртэлх хувьсах хүчдэлийн эх үүсвэрийг GreenPAK -ийн ADC модульд холбож, бусадтай харьцуулахад хамгийн өндөр хүчдэлтэй эх үүсвэрийг сонгох боломжтой дотоод зохион байгуулалттай холбосон болно. Дотоод логик нь энэ мэдээллийг харуулах эсвэл цаашид боловсруулахад зориулагдсан болно.

Энэхүү дизайн нь GreenPAK SLG46620G бүтээгдэхүүн дээр суурилсан бөгөөд энэ нь програмд шаардлагатай бүх аналог болон дижитал барилгын блокуудыг багтаасан болно. Энэ тохиолдолд массивыг GreenPAK IC -ээс шууд удирддаг ADG508 аналог мультиплексор ашиглан сканнерддаг.

Гаралтын мэдээлэл нь хамгийн их хүчдэл дэх хүчдэлийн эх үүсвэрийн дугаартай тохирч буй 3 битийн дижитал тоо юм. Энэхүү мэдээллийг авах шууд арга бол 7 сегментийн дэлгэцийн тусламжтайгаар дугаарыг харуулах явдал юм. SLG46620G-ийн дижитал гаралтыг Reference-д тайлбарласан GreenPAK шийдэл гэх мэт 7 сегментийн дэлгэцийн драйвер эсвэл 74LS47 IC-тэй холбох замаар үүнийг хялбархан хийж болно.

Үзүүлсэн схем нь хамгийн их хүчдэлийг хайж байна. Загварыг хамгийн бага хүчдэлийн илрүүлэгч болгохын тулд аналог мультиплексор ба GreenPAK аналог оролтын хооронд энгийн урьдчилан тохируулах хэлхээг нэмж, мультиплексчийн гаралтыг 1 В-ийн жишиг хүчдэлээс хасах ёстой.

Алхам 2: Үйл ажиллагааны зарчим

Энэхүү загвар нь хамгийн их хүчдэлтэй эх үүсвэрийг сонгох зорилготой тул хамгийн сүүлчийн хамгийн их утгыг хадгалж, оролтын дараагийн утгатай харьцуулж (скан дахь дараагийн хүчдэлийн эх үүсвэрт хамаарах) харьцуулахын тулд бүхэл массив дээр скан хийгддэг.

Дараахь зүйлд бид бүх оролтын дагуу "скан хийх" эсвэл "давталт" гэж үзэх олон талт дарааллыг авч үзэх болно.

Хоёр утгыг харьцуулах нь ACMP бүрэлдэхүүн хэсгүүдийн тусламжтайгаар хийгддэггүй (гэхдээ SLG46620G -д байдаг), харин утгуудыг тоон хэлбэрт оруулсны дараа DCMP модулийн тусламжтайгаар хийгддэг. Энэ бол лавлагаа номонд дурдсан дэвшилтэт, боловсронгуй техник юм.

Зураг 2 -т SLG46620G энэ загварт хэрхэн бүтэцлэгдсэнийг харуулав.

Аналог оролтын дохио нь 1-ийн ашиг бүхий PGA бүрэлдэхүүн хэсгээр дамжуулан ADC оролт руу ордог. Оролтын хүчдэлийг 0-1 В хүртэл зураглахад зориулагдсан урд талын агааржуулагчтай хамгийн сайн тохирох хувилбарыг олж авах боломжтой. GreenPAK ADC модулийн хүрээ.

ADC нь нэг төгсгөлийн горимд ажилладаг бөгөөд аналог дохиог 8 битийн дижитал код болгон хөрвүүлдэг бөгөөд үүнийг DCMP модульд шилжүүлдэг. Дижитал кодыг ADC/FSM буфер хэлбэрээр тохируулсан SPI блок руу оруулах бөгөөд дижитал кодыг хадгалж, дараагийн импульс SPI CLK оролтод ирэх хүртэл өөрчлөгдөхгүй. Зориулалтын логик блок нь SPI CLK оролтыг хөтөлдөг болохыг анхаарна уу. Энэ хэсгийг зөв ажиллуулах үүрэгтэй "үндсэн" логик учраас бид энэ хэсгийг дараа нь судлах болно. Шинэ дижитал код нь бодит оролтын хүчдэлд хамаарах тохиолдолд л SPI модульд хадгалагддаг.

DCMP бүрэлдэхүүн хэсэг нь одоогийн ADC -ийн өгөгдлийг SPI блокт хадгалагдсан хамгийн сүүлийн ялагчтай (хамгийн сүүлд олдсон) харьцуулах зорилгоор ашигладаг. Шинэ ADC өгөгдөл өмнөх өгөгдлөөс их байвал энэ нь OUT+ гаралт дээр импульс үүсгэх болно. Бид OUT+ дохиог ашиглан SPI блокыг шинэ ялагчаар шинэчилдэг.

Дэлхийн цагийн дохио нь ADC -ийн хөрвүүлэлт, ерөнхий цагийг удирддаг. Хөрвүүлэлт хийсний дараа ADC -ийн зэрэгцээ өгөгдлийн гаралттай уялдуулан ADC -ийн INT гаралтын дохионы импульс. Бид INT гаралтыг мөн Matrix1 дээр DFF-ийн хэрэгжүүлсэн 3 битийн хоёртын тоолуурыг нэмэгдүүлэх зорилгоор ашигладаг бөгөөд энэ нь гурван шалтгаанаар ашигтай байдаг.

1. Тоолуурын гаралтын шугамууд нь гадаад аналог мультиплексор руу ханддаг бөгөөд ингэснээр ADC -д дараагийн оролтын хүчдэлийг өгдөг;

2. Скан хийх явцад түр зуурын ялагчийг хадгалахын тулд тооллогыг 3 битийн бүртгэлд (Matrix1-д хэрэгжүүлсэн) хөлдөөсөн;

3. Скан хийж дуусмагц тооллогын хоёр дахь 3 битийн бүртгэлийг (Matrix0-д хэрэгжүүлсэн) шинэчлэхийн тулд тайлдаг.

Алхам 3: Логик хэрэгжилт

ADC модуль нь оролтын бүх хүчдэлийн хөрвүүлсэн өгөгдлийг дараалан дараалан өгдөг. Multiplexer -ийг 0b111 (аравтын бутархай 7) хаягаар тоолсны дараа тоолуур нь 0b000 (аравтын бутархай 0) руу шилжиж оролтын хүчдэлийн шинэ хайлтыг эхлүүлнэ.

Скан хийх явцад зэрэгцээ өгөгдлийн гаралт хүчинтэй байх үед ADC INT гаралтын дохио үүсдэг. Энэ дохио импульсийн үед аналог мультиплексор нь PGA -ийг харгалзах хүчдэлээр хангаж дараагийн оролт руу шилжих ёстой. Тиймээс ADC INT гаралт нь 3-битийн зэрэгцээ гаралтын үг нь гадаад аналог мультиплексор руу шууд ханддаг Зураг 2-ийн 3 битийн хоёртын тоолуурын шууд цагны дохио юм (Зураг 1-д "V сонгох").

Оролтын хүчдэл дараах харьцаатай байх ёстой жишээг авч үзье.

a) V0 <V1 <V2

b) V2> V3, V4

в) V5> V2

Зураг 3 нь хамгийн их шийдвэр гаргах механизмд оролцож буй гол дохиог харуулав.

Өгөгдөл нь эцсийн байдлаар SPI буферийн бүртгэлд INT импульсийн синхрон байдлаар ордог тул SPI буферийн агуулгыг ADC -ийн дараагийн хөрвүүлэлтийн үр дүнтэй харьцуулах цонх байдаг. Энэхүү тодорхой цаг хугацаа нь DCMP гаралт дээр OUT+ импульс үүсгэхэд хүргэдэг. Бид эдгээр импульсийн давуу талыг ашиглан SPI буферийн бүртгэлд шинэ утгуудыг ачаалах боломжтой.

Өмнөх Зураг дээрх SPI буфер өгөгдлийн шугамаас харахад SPI бүртгэл нь үргэлж 8 оролтын хамгийн их утгыг агуулдаг бөгөөд үүнийг DCMP модуль илүү том утгыг илрүүлэх үед л шинэчилдэг. OUT+ гаралтын шугам, дутуу импульс нь V2 -ийг V5 -тэй харьцуулахад бүртгэлд хадгалагдаж үлдэхэд хүргэдэг).

Алхам 4: Түгжрэлийг шийдвэрлэх

Хэрэв хэрэгжүүлсэн логик нь дээр дурдсантай адил байвал бид мухардмал байдалд орох нь ойлгомжтой: систем нь SPI -ийн буфер бүртгэлд хадгалагдаж буй хэмжээнээс харгалзах хүчдэлийг л илрүүлэх чадвартай.

Хэрэв энэ хүчдэл буурч, үүнээс доогуур оролттой оролт нь хамгийн өндөр болох юм бол үүнийг хэзээ ч илрүүлэхгүй. тодорхой байдал.

Давталт 2 хийх үед V3 буурч, V1 нь бодит хамгийн их хүчдэл болно. Гэхдээ DCMP модуль нь импульс өгдөггүй, учир нь SPI буферийн бүртгэлд хадгалагдсан өгөгдөл (0.6 В -тэй тэнцүү) нь V1 (0.4 V) харгалзах хэмжээнээс том байна.

Дараа нь систем нь "туйлын" хамгийн их хайгчийн үүргийг гүйцэтгэдэг бөгөөд гаралтыг зөв шинэчилдэггүй.

Энэ асуудлыг даван туулах сайхан арга бол систем бүх сувгийн санал авах мөчлөгийг дуусгасны дараа өгөгдлийг SPI Орчны Бүртгэлд дахин ачаалах явдал юм.

Үнэн хэрэгтээ хэрэв энэ оролтын хүчдэл хамгийн өндөр хэвээр байвал юу ч өөрчлөгдөхгүй бөгөөд хяналт аюулгүй үргэлжилнэ (дээрх Зураг 4 -ийг үзвэл энэ нь 0 ба 1 давталтын давталтын жишээ юм). Нөгөөтэйгүүр, хэрэв тухайн оролтын хүчдэл санамсаргүй байдлаар өөр оролтоос бага утга хүртэл буурсан бол утгыг дахин ачаалах нь DCMP модульд шинэ дээд утгатай харьцуулах үед OUT+ импульс үүсгэх боломжийг олгодог. 2 ба 3 давталтын давталтын тохиолдол).

Асуудлыг даван туулахын тулд нэг логик хэлхээ шаардлагатай болно. Энэ нь давталт нь хамгийн их оролтод хүрэх үед SPI бүрэлдэхүүн хэсэгт цагийн дохио өгөх ёстой бөгөөд ингэснээр шинэчлэгдсэн өгөгдлийн үгээ SPI Орчны Бүртгэлд дахин ачаалах болно. Үүнийг доорх 7.2 ба 7.6 -р хэсгүүдэд хэлэлцэх болно.

Алхам 5: Төхөөрөмжийн тохиргоо - Matrix0 хэлхээ

SLG46620G нь 2 -р зурагт үзүүлсэн шиг хоёр матрицын блоктой байна. Дараах зургууд нь тухайн төхөөрөмжийн тохиргоог харуулав.

Хэлхээний дээд хэсэг нь 3 DFF (DFF0, DFF1 ба DFF2) ашиглан хийгдсэн "Loop Register" юм. Оролтын мультиплексор бүрийн давталт бүрийн дараа 7 сегментийн дэлгэцийн драйвер руу "ялагч" гэсэн хоёртын дугаарыг илгээдэг бөгөөд энэ нь сүүлийн хайлтын хамгийн өндөр хүчдэлтэй оролт юм. DFF -ийн цаг болон өгөгдөл хоёулаа P12, P13, P14, P15 портуудаар дамжуулан Matrix1 -д хэрэгжүүлсэн логикоос үүдэлтэй.

Доод хэсэг нь Pin 8 ба PGA оролттой аналог урд хэсэг бөгөөд x1 олзтой. ADC INT гаралт нь SPI -ийн цагийн логик болон Матриц1 руу P0 портоор дамждаг бөгөөд энэ нь тоолуурыг ажиллуулах цагийн дохио болдог.

ADC ба SPI -ийн зэрэгцээ өгөгдөл гаралтыг NET11 ба NET15 гэж тэмдэглэсэн бөгөөд Matrix1 дэх DCMP бүрэлдэхүүн хэсэгт холбох болно.

Алхам 6: Төхөөрөмжийн тохиргоо - SPI цагны логик

"Логик хэрэгжилт" хэсэгт өмнө дурдсанчлан SPI Орчны Бүртгэлийг хадгалагдсан бодит үнэ болон ADC хувиргах шинэ өгөгдөлтэй харьцуулах нь DCMP OUT+ гаралт дээр импульс үүсгэх бүрт шинэчлэгддэг.

Хэрэв энэ дохиог ADC INT гаралттай AND-засварласан бол дохионы бүрэн бүтэн байдлыг хангана. Энэ нь аливаа огцом өсөлт, хуурамч өдөөлтөөс зайлсхийх болно.

Түгжрэлийг даван туулахын тулд давталтын бодит ялагчийн өгөгдөлд хүрэх үед SPI Орчуулагчийг шинэчлэх шаардлагатай гэдгийг бид онцлон тэмдэглэв.

Дараа нь SPI -ийг зөв хэмжих гурван дохио тоглоомонд байна:

1. ADC INT гаралт (LUT0-IN1)

2. DCMP OUT+ гаралт (P10 портоор LUT0-IN0)

3. Тоолол нь түгжээний дохиотой тэнцэнэ (P11 портоор LUT0-IN2)

Эхний хоёр нь AND-ed ба аль аль нь OR-ed-тэй бөгөөд сүүлийнх нь LUT0-д байдаг бөгөөд тэдгээрийн хэрэгжилтийг Зураг 6-д үзүүлснээр тохируулсан болно.

Алхам 7: Төхөөрөмжийн тохиргоо - Matrix0 бүрэлдэхүүн хэсгүүдийн шинж чанар

Зураг 7-10-д Matrix0-д хамаарах үлдсэн эд ангиудын үл хөдлөх хөрөнгийн цонхыг харуулав.

Алхам 8: Төхөөрөмжийн тохиргоо - Matrix1 хэлхээ

Алхам 9: Төхөөрөмжийн тохиргоо - 3 битийн хоёртын тоолуур

Хэлхээний дээд хэсэгт логик элементүүд байдаг бөгөөд голчлон өмнө дурдсанчлан ADC INT гаралтаар ажилладаг 3 битийн хоёртын тоолуур байдаг. Энэхүү тоолуурыг Зураг 12 -т үзүүлсэн нэлээд "стандарт" схемийн дагуу хэрэгжүүлсэн болно.

Энэхүү тоолуурыг манай загварт Flip-Flops DFF9, DFF10, DFF11 ба INV1, LUT4, LUT8-ийн тусламжтайгаар хэрэгжүүлдэг. DFF9 гаралт нь LSB, DFF11 нь MSB бөгөөд Зураг 13 -т үзүүлсэн болно.

LUT4 нь XOR хэлбэрээр тохируулагдсан бол LUT8 нь Зураг 12-ийн AND-XOR логикийг гүйцэтгэдэг.

Тоологчийн гаралт нь гадаад аналог мультиплексорыг шийдвэрлэхийн тулд гурван дижитал гаралтын зүү рүү ордог.

LUT10 нь скан хийж дуусаад лангууны кодыг тайлж, импульсийг Matrix0 руу DLY8 болон P12 портоор дамжуулдаг. Үүнийг тоолуурын гаралтыг AND-д оруулснаар л хийдэг бөгөөд ингэснээр 7 dec (0b111 хоёртын, давталтын төгсгөл) дугаарын кодыг тайлдаг.

Алхам 10: Төхөөрөмжийн тохиргоо - 3 битийн харьцуулах логик

Зураг 15 -д одоогийн "ялагч" хаягаар давталт давтагдаж байгааг илрүүлэх хэлхээг харуулав. Энэ тохиолдолд, дээр дурдсанчлан дижитал импульс нь одоогийн ADC-ийн үр дүнг дахин ачаалахад хүргэж болзошгүй хүндрэлийг шийдвэрлэх ёстой.

"Ялагч" хаягийг Matrix1 -ийн түр бүртгэлд хадгалдаг (доороос үзнэ үү), одоогийн хаягийг хоёртын тоолуур гаргадаг.

XNOR хаалга нь оролт хоёулаа тэнцүү үед үнэн (логик 1 эсвэл "өндөр") гаралтыг өгдөг. Энэ дохиог бүх битүүдэд (LUT9) өгөх нь хоёртын код хоёулаа ижил байх үед импульс өгдөг. Parit шалгагч болох XOR хаалганы талаарх дэлгэрэнгүй мэдээллийг лавлагаанаас авах боломжтой.

'Counter-equals-Latch' дохиог Matrix0 руу P11 портоор дамжуулдаг.

Алхам 11: Төхөөрөмжийн тохиргоо - Дижитал харьцуулах логик ба түр бүртгэл

Зураг 11-ийн доод хэсэгт (Зураг 16-д онцлон харуулав) энэ дизайны шийдвэр гаргах хэсэг болох DCMP блокыг харуулав.

DFF6, 7, 8 нь давталт ажиллаж байх үед "ялагч" гэсэн түр оролтын дугаарыг хадгалахын тулд 3 битийн бүртгэл үүсгэдэг. Flip-Flops-ийн оролт нь 3-битийн хоёртын тоолуурын гаралт бөгөөд үүнийг Зураг 11-ийн дэлхийн Matrix1 хэлхээнд харуулав.

Энэ бүртгэлийн гаралт нь 7 сегментийн дэлгэцийг шууд удирдах боломжгүй, учир нь энд хадгалагдсан утга нь скан хийх явцад өөрчлөгддөг бөгөөд үүнийг зөвхөн хайлтын төгсгөлд "хүчинтэй" гэж үзэх ёстой.

Ийм учраас түр бүртгэлийн гаралтууд нь матриц хоорондын P13, P14, P15 портуудаар дамжуулан Matrix0-ийн Loop Register-тэй холбогддог.

ADC-SPI-ийн харьцуулалтын үр дүнд шинэ максимум гарч ирэх үед түр зуурын бүртгэлийг DCMP OUT+ гаралтаар цагжиж байгааг Зураг 16-д ажиглах нь чухал юм.

Үүнтэй ижил OUT+ дохиог Matrix0, SPI CLK Logic руу P10 портоор дамжуулдаг.

Алхам 12: Төхөөрөмжийн тохиргоо - Matrix1 бүрэлдэхүүн хэсгүүдийн шинж чанарууд

Зураг 17-19-д Matrix1-ийн харьяалагддаг цонхны бүрэлдэхүүн хэсгүүдийг харуулав.

Алхам 13: Үр дүн

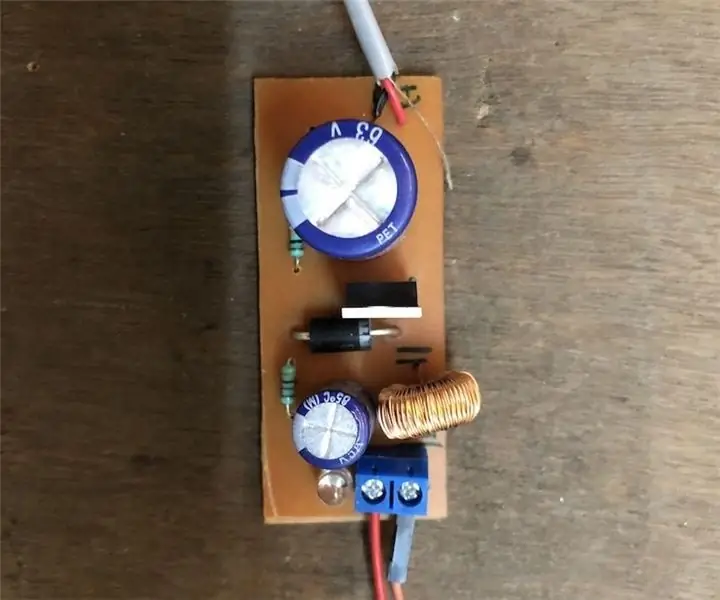

Хэрэгжилтийг шалгахын тулд үнэлгээний самбарын загварыг бүтээсэн бөгөөд 8 аналог оролтын хүчдэлийг TrimPots -тэй резистор хуваагчаас олж авдаг (Зураг 20 -д үзүүлсэн шиг).

Ашигласан мультиплексор нь ADG508 бөгөөд нэг тэжээлээр (12 В) ажиллах боломжтой хэсэг юм.

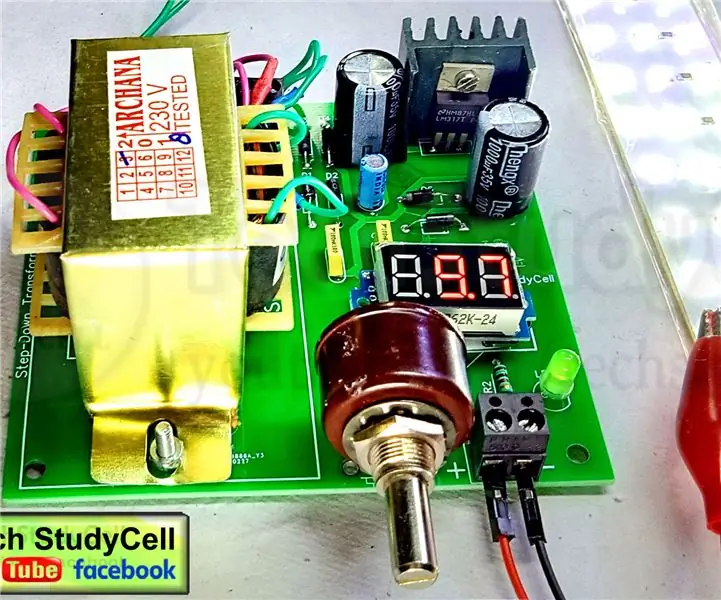

7 сегментийн дэлгэцийн драйвер нь 74LS47 юм. Энэ нь зэрэгцээ оролтын үгийг тайлж, 7 анодтой нийтлэг анодын дэлгэцийг шууд удирддаг.

Үнэлгээний самбар нь Зураг 21-д үзүүлсэн шиг өргөтгөлийн холбогч дээр GreenPAK дэвшилтэт хөгжлийн платформ руу шууд залгах 2x10 хэмжээтэй тэгш өнцөгт холбогчтой.

GreenPAK -ийн дэвшилтэт хөгжлийн платформтой хослуулан хурдан шалгахын тулд дохионы хэмжилтийг хийхэд маш хялбар болгодог. Жишээлбэл, Зураг 22 -т HP 54620A логик анализаторын авсан дохионуудын багцыг (тус бүр CLOCK, ADC INT гаралт, DCMP OUT+ гаралт) харуулав. Долгионы хэлбэр нь OUT+ дохионы өсөн нэмэгдэж буй ирмэгээр өдөөгддөг ('A> B' гэж тэмдэглэгдсэн хамрах хүрээ дээр), иймээс аналог оролтын дунд шинэ хамгийн их хүчдэл илрэх үед энэ нь долгионы хэлбэр юм. Үнэн хэрэгтээ 22 -р зурагт үзүүлсэн харгалзах хүчдэлийг нэмэгдүүлэхийн тулд Үнэлгээний зөвлөлийн TrimPots -ийн аль нэгийг эргүүлснээр олж авсан болно.

Зураг 23 -т Үнэлгээний зөвлөлийн схемийг үзүүлэв.

Дүгнэлт

Энэхүү зааварт бид олон сувгийн хяналтын системд нийтлэг нэмэлт болгон ашиглах найман сувгийн хамгийн их (эсвэл мин) хүчдэлийн илрүүлэгчийг ашигласан. Энэхүү танилцуулсан арга нь GreenPAK -ийн бүрэлдэхүүн хэсгүүдийн дэвшилтэт шинж чанаруудыг ашиглаж, аналог болон дижитал функцийг нэг чипт хэрхэн нэгтгэх боломжтойг харуулж байна. Хэд хэдэн арилжааны IC -ийг Dialog GreenPAK -ээр сольж болох бөгөөд ингэснээр програмын хэмжээ, зардлыг бууруулах боломжтой болно.

Зөвлөмж болгож буй:

Өндөр хүчдэлийн батерейны хүчдэлийн хяналт: 3 алхам (зурагтай)

Өндөр хүчдэлийн батерейны хүчдэлийн хяналт: Энэхүү гарын авлагад би цахилгаан хавтангийнхаа зайны хүчдэлийн мониторыг хэрхэн бүтээсэнээ тайлбарлах болно. Үүнийг хүссэнээрээ холбоод зайгаа ердөө хоёр утас холбоно уу (Gnd ба Vcc). Энэхүү гарын авлагад таны батерейны хүчдэл 30 вольтоос давсан гэж үзжээ

DC - DC хүчдэлийн алхам доош шилжих горим Бак хүчдэлийн хөрвүүлэгч (LM2576/LM2596): 4 алхам

DC-DC хүчдэлийн алхам доош шилжих горим Бак хүчдэлийн хөрвүүлэгч (LM2576/LM2596): Өндөр үр ашигтай Бак хөрвүүлэгч хийх нь маш хэцүү ажил бөгөөд туршлагатай инженерүүд хүртэл олон загварыг зөв болгохыг шаарддаг. Энэ нь хүчдэлийг бууруулдаг DC-DC гүйдлийн хүч хувиргагч юм

LM317 хүчдэлийн зохицуулагчийг ашиглан тохируулах хүчдэлийн тогтмол гүйдлийн тэжээл: 10 алхам

LM317 хүчдэлийн зохицуулагчийг ашиглан тохируулж хүчдэлийн тогтмол гүйдлийн цахилгаан хангамж: Энэ төсөлд би LM317 цахилгаан хангамжийн хэлхээний диаграмм бүхий LM317 IC ашиглан энгийн тохируулгатай хүчдэлийн тогтмол гүйдлийн тэжээлийг зохион бүтээсэн болно. Энэ хэлхээ нь суурилуулсан гүүр Шулуутгагчтай тул бид 220V/110V AC тэжээлийг оролт дээр шууд холбох боломжтой

Компьютер эсвэл гэрийн театрт зориулсан 8 сувгийн аналог өсгөгч: 12 алхам (зурагтай)

Компьютер эсвэл гэрийн театрт зориулсан 8 сувгийн аналог өсгөгч: Энэ бол миний анхны зааварчилгаа юм. Би танд тусдаа аналог гаралттай компьютер эсвэл аудио системд зориулж 8 сувгийн өсгөгч хэрхэн хийхийг зааж өгөх болно, үүнийг ширээний компьютер дээрээ ашиглаж, кино үзэх, HD хөгжим сонсох, тоглоом тоглох гэх мэт

Пикакс дээр суурилсан дижитал термометр нь Макс ба Мин: 13 алхамтай

Picaxe дээр суурилсан дижитал термометр нь Макс ба Мин: (Мессеж үлдээгээрэй, гэхдээ битгий шүүмжлээрэй, энэ бол миний анхны заавар !!) Энэ нь хямд бөгөөд ашиглахад хялбар тул Picaxe чип дээр суурилсан болно. Хэрэв энэ нь зориулагдсан бол