Агуулгын хүснэгт:

- Зохиолч John Day day@howwhatproduce.com.

- Public 2024-01-30 11:02.

- Хамгийн сүүлд өөрчлөгдсөн 2025-01-23 15:00.

UART нь бүх нийтийн асинхрон хүлээн авагч дамжуулагч гэсэн үг юм. Энэ бол хамгийн түгээмэл бөгөөд хамгийн энгийн цуваа холбооны протокол юм. Энэ зааварчилгаанд та VHDL дээр UART модулийг хэрхэн зохион бүтээх талаар сурах болно.

Алхам 1: UART гэж юу вэ?

Төрөл бүрийн дагалдах төхөөрөмжүүдтэй холбогдохын тулд процессорууд эсвэл хянагчид ихэвчлэн UART холболтыг ашигладаг. Энэ бол энгийн бөгөөд хурдан цуваа холбоо юм. UART нь бараг бүх процессоруудад хамгийн бага шаардлага байдаг тул тэдгээрийг дахин ашиглах, нэгтгэхэд хялбар болгох үүднээс VHDL эсвэл Verilog дахь Soft IP цөм болгон бүтээдэг.

Алхам 2: Техникийн үзүүлэлтүүд

Зохион бүтээгдсэн UART -ийн техникийн үзүүлэлтүүдийг доор өгөв.

* UART стандарт дохио.

* 600-115200 хооронд тохируулагдах baud rate.

* Дээж авах = 8x @хүлээн авагч

* FPGA батлагдсан дизайн - Xilinx Artix 7 самбар дээр.

* UART -ийн дагалдах төхөөрөмжүүд дээр туршиж үзсэн, Hyperterminal амжилттай болсон - бүх баудратууд

Алхам 3: Дизайн арга

-

Бид 3 модулийг зохион бүтээх бөгөөд дараа нь нэгтгэн UART -ийг дуусгах болно.

- Дамжуулагч модуль: Өгөгдлийн цуваа дамжуулалтыг хариуцдаг

- Хүлээн авагч модуль: Цуваа өгөгдөл хүлээн авахад анхаарал тавьдаг

- Baud генераторын модуль: Baud цаг үйлдвэрлэхэд анхаарал тавьдаг.

- Baud генераторын модулийг динамикаар тохируулах боломжтой. Энэ нь хүссэн хурдны дагуу үндсэн цагаас хоёр бауд цаг үүсгэдэг. Нэг нь дамжуулагч, нөгөө нь хүлээн авагчийн хувьд.

- Хүлээн авагчийн модуль нь хүлээн авах явцад гарсан алдааны магадлалыг багасгахын тулд дээж авах хурдыг 8x ашигладаг, өөрөөр хэлбэл хүлээн авагчийн бодын цаг нь 8х дамжуулагч бауд цаг юм.

- Хяналтын дохио нь дамжуулах, хүлээн авах, түүнчлэн тасалдлын дохиог хянах боломжтой.

- Стандарт UART цуваа интерфэйс нь парит битгүй, нэг зогсолт ба эхлэх бит, 8 өгөгдлийн бит юм.

- Параллель өгөгдлийг UART -ээс тэжээж, хүлээн авдаг процессор эсвэл хянагчтай харьцах зэрэгцээ интерфейс.

Алхам 4: Загварчлалын үр дүн

Алхам 5: Хавсаргасан файлууд

* UART дамжуулагч модуль -vhd файл

* UART хүлээн авагч модуль - vhd файл

* Baud генераторын модуль - vhd файл

* UART модуль - Дээрх модулийг нэгтгэсэн үндсэн дээд модуль - vhd файл

* UART IP Core -ийн бүрэн баримт бичиг - pdf

Асууж лавлах зүйл байвал надтай холбоо бариарай.

Миту Раж

намайг дага:

Асуулт авахыг хүсвэл iammituraj@gmail.com хаягаар холбогдоно уу

Зөвлөмж болгож буй:

MODBUS RTU дахь үйлдвэрлэлийн HMI ба Arduinos: 4 алхам

MODBUS RTU дахь Industrial HMI ба Arduinos: Энэхүү зааварчилгаанд би үйлдвэрлэлийн HMI (COOLMAY MT6070H, 150EUROS), Arduino CLONE DIY (10EUROS) ба Arduino UNO (10EUROS) хоорондын харилцааны жишээг тайлбарлах болно. Сүлжээ нь тусгай, хүчирхэг, үйлдвэрлэлийн протоколоор ажиллах болно

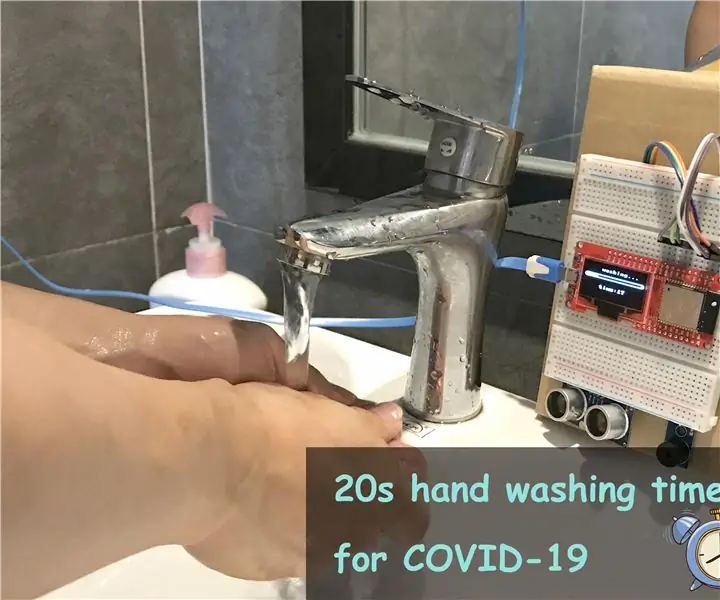

COVID-19-д зориулсан 20 дахь хоёр дахь гар угаах таймер: 6 алхам (зурагтай)

COVID-19-д зориулсан хоёр дахь гар угаах таймер: Дэлхий даяар COVID-19 тархах тусам бид нүүрээ бага багаар цуглуулж, гараа илүү олон удаа угааж өөрийгөө хамгаалах ёстой. гараа зөв угааж болохгүй. Гараа хэрхэн зөв угаах вэ? W

VHDL дээр програмчлагдах тасалдлын хянагчийн дизайн: 4 алхам

VHDL -д програмчлагдах тасалдлын хянагчийн загвар: Энэ блог дээр надад ямар төрлийн хариулт өгч байгаад би сэтгэл дундуур байна. Миний блогоор зочилж, мэдлэгээ та бүхэнтэй хуваалцах урам зориг өгсөн залуусдаа баярлалаа. Энэ удаад би бүх SOC -д харагддаг өөр нэг сонирхолтой модулийн загварыг танилцуулах болно - Interrupt C

VHDL дээрх I2C мастер дизайн: 5 алхам

VHDL дээрх I2C мастер дизайн

VHDL ба Verilog дээр энгийн VGA хянагчийн дизайн: 5 алхам

VHDL ба Verilog дээрх энгийн VGA хянагчийн загвар: Энэхүү зааварчилгаанд бид RTL дээр энгийн VGA хянагч зохион бүтээх гэж байна. VGA хянагч нь VGA дэлгэцийг удирдах зориулалттай дижитал хэлхээ юм. Энэ нь харуулах хүрээг харуулсан Frame Buffer (VGA санах ой) -оос уншиж, шаардлагатай зүйлийг үүсгэдэг