Агуулгын хүснэгт:

- Алхам 1: Дахин хэвийсэн үе шат

- Алхам 2: Одоогийн мэдрэгч эсэргүүцэл

- Алхам 3: Цахилгаан дамжуулагчийн өсгөгч

- Алхам 4: Хэмжих хэрэгслийн өсгөгч

- Алхам 5: Оролтын үе шат ба шалгалт тохируулга

- Алхам 6: Нарийвчилсан зүйл: Спектрийн алдагдал (DC)

- Алхам 7: Нарийвчилсан зүйл: Спектрийн алдагдал (AC)

- Алхам 8: Дэвшилтэт зүйл: онолын ашиг-хүчин зүйл

- Алхам 9: Нарийвчилсан зүйл: ТХГН -ийн Shift

- Зохиолч John Day day@howwhatproduce.com.

- Public 2024-01-30 11:02.

- Хамгийн сүүлд өөрчлөгдсөн 2025-06-01 06:09.

Би биеийн бүтцийг хэмжих зорилгоор био импеданс анализатор хийх сонирхолтой байсан бөгөөд санамсаргүй хайлтаар Вандербилт их сургуулийн 2015 оны биоанагаахын багажийн ангийн загварыг хайж байсан. Би дизайныг боловсруулж, бага зэрэг сайжруулсан. Би олж мэдсэн зүйлээ та бүхэнтэй хуваалцахыг хүсч байна. Хэрэв ямар нэгэн зүйл ойлгомжгүй байгаа бол энэ "алхах" хэсгээс ашиглаж болох зүйлээ аваарай. Хэзээ нэгэн цагт би бодлоо илүү уялдаатай хэлбэрээр бичиж болох ч одоогоор эндээс олж харсан зүйлээ ашиглаж болно гэж найдаж байна. (Хэрэв та үүнийг бичиж, сайжруулж чадна гэж бодож байвал тавтай морилно уу)

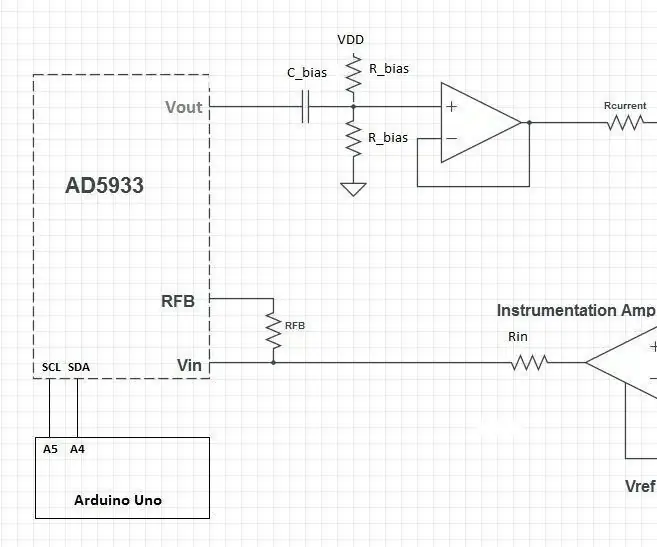

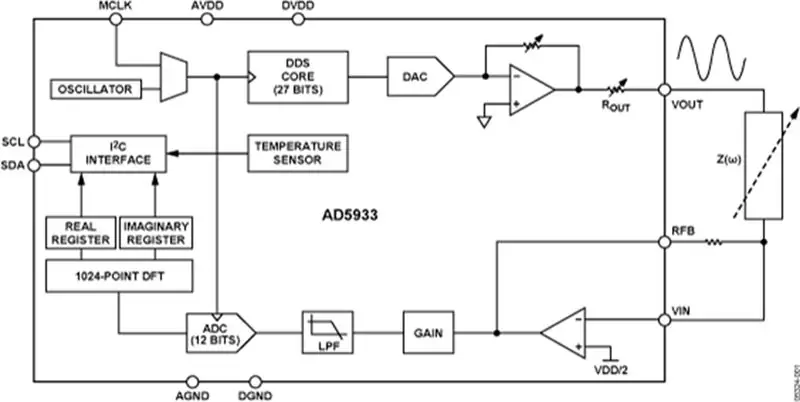

Тедди

Энэхүү загвар нь AD5933 чип болон AD5933-ийг их биетэй холбох интерфэйсийн тусгай аналог урд хэсэг (AFE) -ээс бүрдэнэ. AD5933 нь хэмжилт хийдэг бөгөөд үр дүнг нь микроконтроллер (жишээлбэл Arduino) боловсруулж болно.

Хэрэв та Arduino-г цахилгаан хангамж болгон ашиглахаар төлөвлөж байгаа бол ашиглалтын болон багаж хэрэгслийн өсгөгч (op-amps ба in-amps) нь "нэг хангамж" гэж нэрлэгддэг хүчдэлийг дэмжиж, төмөр замаас төмөр замын онцлогтой эсэхийг шалгаарай.

(Дараахь тохиолдолд би 5V -ийн тэжээлийн хангамж (Arduino -аас) болон AD5933 дээрх Range 1 тохиргоог ашиглах болно.)

Алхам 1: Дахин хэвийсэн үе шат

AFE-ийн эхний хэсэг бол дахин хэвийсэн үе шат юм. Гаралтын хүчдэлийн дохио нь тэжээлийн хүчдэлийн хязгаарын дунд төвлөрдөггүй (VDD/2). Үүнийг конденсатор ашиглан дохионы DC хэсгийг хааж хүчдэл хуваагуураар дамжуулж DC -ийн офсетыг буцааж дохио руу оруулна.

Хоёр дахин хэвийсэн эсэргүүцэл нь ижил байвал ямар ч үнэ цэнэтэй байж болно. Малгайны тодорхой утга нь бас чухал биш юм.

Дахин хэвийх үе нь өндөр дамжуулагч шүүлтүүр шиг ажилладаг тул таслах давтамжтай байдаг.

f_c = 1 / (2 * pi * (0.5 * R) * C)

Таслах давтамж нь ашиглахаар төлөвлөж буй хамгийн бага давтамжаас хэдэн арван жил доогуур байгаа эсэхийг шалгаарай. Хэрэв та програм дээрээ 1 кГц-ийг ашиглахаар төлөвлөж байгаа бол 1-10 Гц-ийн дарааллаар таслах давтамжийг өгөх хязгаар ба эсэргүүцлийн утгыг сонгох хэрэгтэй.

Энэ үе шатны сүүлчийн хэсэг нь хүчдэлийн дагалдагч байхаар тохируулсан op-amp юм. Энэ нь резисторын утга нь дараагийн шатанд саад болохгүй гэдгийг баталгаажуулах явдал юм

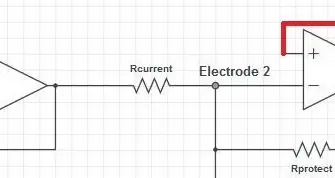

Алхам 2: Одоогийн мэдрэгч эсэргүүцэл

Дараагийн шатны эхний хэсэг нь одоогийн мэдрэгч резистор юм. Энэ резистороор дамжих гүйдэл нь өсгөгч нь биеэр дамжин өнгөрөхийг хичээх болно. Одоогийн гүйдэл нь IEC6060-1 аюулгүй байдлын стандартад нийцэж байгаа эсэхийг шалгаарай.

1 кГц давтамжаас доогуур биеэр хамгийн ихдээ 10 микроАмпс (RMS) нэвтрэхийг зөвшөөрдөг. 1 кГц -ээс дээш давтамжтай үед дараахь тэгшитгэл нь зөвшөөрөгдсөн хамгийн их гүйдлийг өгдөг.

Хамгийн их гүйдлийн гүйдэл <(кГц дэх хамгийн бага давтамж) * 10 микроАмпс (RMS)

AC дохионы оргил далайц ба түүний RMS утгын хоорондын хамаарал нь: Оргил = sqrt (2) * RMS. (10 microAmps RMS нь 14 microAmps оргил далайцтай тохирч байна)

Эсэргүүцлийн тухай Ом -ийн хуулийг ашиглан бид аюулгүй байдлын стандартад нийцсэн эсэргүүцлийн утгыг тооцоолж болно. Бид AD5933 -ийн өдөөх хүчдэл ба хамгийн их гүйдлийн утгыг ашигладаг.

U = R * I => R = U / I

Жишээлбэл Range 1 тохиргоог ашиглан Upeak = 3V / 2 = 1.5V (эсвэл 1V @3.3V)

Дээрээс 14 microAmp оргил утгыг ашигласнаар би дор хаяж 107 кОм эсэргүүцлийн утгыг олж авдаг

Ашигласан материал:

* Аналог төхөөрөмжүүд: "Биеийн элэгдэлд орсон системд зориулсан био-эсэргүүцлийн хэлхээний дизайн"

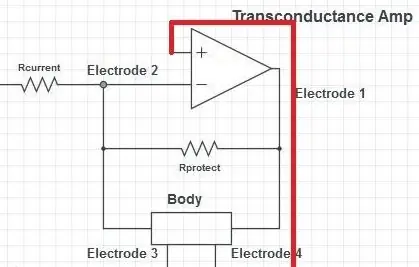

Алхам 3: Цахилгаан дамжуулагчийн өсгөгч

Одоогийн мэдрэгч эсэргүүцэгчийн дараа сөрөг санал хүсэлтийн тохиргоонд op-amp байна. Энэ бол Loop-in-the-Loop гэж нэрлэгддэг тохиргоо юм. Оп-өсгөгчийн эерэг оролтын терминал нь VDD/2 хүчдэлтэй холбогдсон байна. Оп-өсгөгч нь өдөөх дохионы эсрэг чиглэлд гаралтыг тохируулахыг оролдох бөгөөд ингэснээр сөрөг терминал дахь хүчдэл VDD/2-тэй тэнцүү байх болно. Энэ нь биеэр гүйдлийг түлхэж, татах хүчийг хардаг.

Оп-өсгөгчийн сөрөг терминалаас авсан гүйдэл бараг тэг байна. Тиймээс одоогийн мэдрэгч резистороор дамжих бүх гүйдэл биеэр дамжих ёстой. Энэ нь энэхүү тохиргоог дамжуулагч дамжуулагч өсгөгч (хүчдэлийн хяналттай гүйдлийн эх үүсвэр гэж нэрлэдэг VCCS) болгодог механизм юм.

Оп-өсгөгч нь биеийн эсэргүүцэл хэт өндөр биш тохиолдолд л гүйдлийг хадгалах боломжтой. Үгүй бол op-amp гаралт нь тэжээлийн хүчдэлд (0 эсвэл 5 V) хамгийн их гарах болно. Хүчдэлийг хадгалах хамгийн дээд хязгаар нь VDD/2 + Upeak (2.5 + 1.5V = 4V @ 5V хангамж) юм. Оп-өсгөгчийн хүчдэлийн хязгаарыг энэ утгаас хасах ёстой, гэхдээ хэрэв op-amp нь төмөр замаас төмөр замын онцлог шинж чанартай бол энэ нь маш бага хэмжээтэй байх болно. Тиймээс op-amp-ийн жолоодож болох хамгийн их эсэргүүцэл нь:

Z <(VDD / 2 + Upeak) / Imax

(Миний тохиргоонд Z <4V / 14 microAmps = 285 kOhms, биеийн эсэргүүцлийн хүрээг хамрах хангалттай хүсэл байна)

Хамгаалалтын резистор нь биетэй (ойролцоогоор 100 кОм) харьцуулахад маш том утгатай (1-1.5 МОм) бөгөөд бүх хэвийн үйлдлүүдийн хувьд энэ нь мэдэгдэхүйц гүйдэл авчрахгүй бөгөөд зэрэгцээ холболтын эсэргүүцэл нь биеийн эсэргүүцэлээр давамгайлдаг. Хэрэв биеийн эсэргүүцэл нэмэгдэх юм бол (жишээлбэл дэвсгэр сулрах болно) гүйдэл нь резистороор дамжих бөгөөд оп-ампаас гарах нь дэвсгэр дээр тааламжгүй хүчдэл үүсгэхгүй.

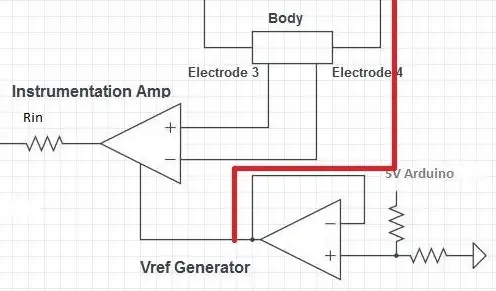

Алхам 4: Хэмжих хэрэгслийн өсгөгч

Дараагийн шат бол биеийн хүчдэлийг хэмжих багажны өсгөгч юм. Биеийн бүх хүчдэл 0V орчим хэлбэлзэж байгаа боловч AD5933 нь оролтын хүчдэлийг эерэг хязгаарт байлгах шаардлагатай байна. Тиймээс өсгөгч нь хэмжсэн хүчдэлийн дохионд VDD/2 тогтмол гүйдлийн офсетыг нэмдэг.

VDD/2 лавлагаа нь хүчдэл хуваагчаар үүсгэгддэг. Аливаа утгын эсэргүүцэгчийг ижилхэн байхад л ашиглаж болно. Хүчдэл хуваагч нь бусад хэлхээний эсэргүүцэлээс хүчдэлийн дагалдагчаар тусгаарлагддаг. Дараа нь хүчдэлийн дагалдагчийн гаралтыг өсгөгч ба дамжуулагч өсгөгч рүү дамжуулж болно.

Алхам 5: Оролтын үе шат ба шалгалт тохируулга

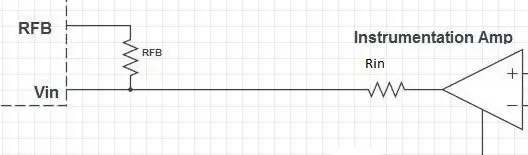

AD5933-ийн оролтын үе нь сөрөг санал хүсэлтийн тохиргоонд op-amp агуулдаг. Хоёр эсэргүүцэл байдаг: нэг нь цуврал (Rin), нөгөө нь зэрэгцээ (RFB). Оп-өсгөгчийн олзыг дараах байдлаар өгнө

A = - RFB / Rin

Оролтын op-amp ба in-amp (ба PGA) -ийн ашиг нь AD5933-ийн ADC руу орж буй дохио нь үргэлж 0V ба VDD-д байгаа эсэхийг шалгах хэрэгтэй.

(Би хүчдэлийн эсэргүүцэл ба эсэргүүцлийн утгыг ашигладаг бөгөөд энэ нь ойролцоогоор A = 0.5 болно)

AD5933 дотор ADC нь хүчдэлийн дохиог a болгон тоон дохио болгон хувиргах болно. 0V-ээс VDD хүртэлх хүчдэлийн хязгаарыг 0-128 (2^7) дижитал муж болгон хөрвүүлнэ. (Энэ талаар баримт бичиг тодорхой болоогүй байгаа боловч [1] дээрх хэсгүүдийг сайтар судалж, миний хийсэн сомын туршилт үүнийг баталж байна.)

DFT модуль дотор үр дүнг бодит болон төсөөллийн бүртгэлд хадгалахаас өмнө өөр масштабтай 256 (1024/4, [1] -ийг үзнэ үү) байна.

Хүчдэлийн дохиог AFE-ээс ADC-д дагаж, өмнө дурдсан масштабтай хүчин зүйлсийг ашиглан ашгийн коэффициентийг тооцоолох боломжтой болно.

g = (VDD * Rcurrent * Rin) / (256 * PGA * Upeak * RFB * 2^7)

Зарим шалгалт тохируулга шаардлагатай байж магадгүй тул математик загварт хамаарахгүй зарим эффектийг харгалзан үзнэ үү. (g = Z / mag, доороос үзнэ үү)

Эсэргүүцлийг одоо тооцоолж болно

Z = g * mag

mag = sqrt (бодит^2 + төсөөлөлтэй^2)

PA = arctan2 (бодит, төсөөлөлтэй) - deltaPA

ТХГН-ийг калибровк хийх шаардлагатай бөгөөд AD5933-ийн давтамжийн функц болох системчилсэн фазын шилжилт байдаг. deltaPA нь давтамжийн зарим шугаман функц байж магадгүй юм.

Эсэргүүцэл ба урвалыг одоо тооцоолж болно

R = Z * cos (PA)

X = Z * sin (PA)

Ашигласан материал: [1] Леонид Мациев, "AD5933 гэх мэт нэг давтамжтай DFT илрүүлэгч дээр суурилсан системийн гүйцэтгэл, олон талт байдлыг сайжруулах", Электроникс 2015, 4, 1-34; doi: 10.3390/электроник 4010001

Алхам 6: Нарийвчилсан зүйл: Спектрийн алдагдал (DC)

Бидний AD5933 -д оруулсан дохио нь хүчдэл/гүйдэл нь цаг хугацааны функц боловч бидний гол сонирхол бол давтамжийн функц болох эсэргүүцэл юм. Цагийн домэйн ба давтамжийн домэйныг хооронд нь хөрвүүлэхийн тулд бид цагийн домэйны дохионы Фурье хувиргалтыг хийх хэрэгтэй. AD5933 нь салангид Фурье хувиргах (DFT) модультай. Бага давтамжтай (ойролцоогоор 10 кГц -ээс доош) үед DFT -ийн бүтцэд нэр томъёо, спектрийн алдагдал нөлөөлдөг. [1] -д тэрээр спектрийн алдагдлыг хэрхэн яаж засах талаар математикаар дамждаг. Үүний мөн чанар нь шүүрдэх давтамжийн алхам бүрт таван (хоёр нэмэх) тогтмолыг тооцоолох явдал юм. Үүнийг хялбархан хийж болно, жишээ нь. програм хангамж дээр Arduino.

Нэвчилт нь хоёр хэлбэртэй байдаг: нэмэлт шинж чанартай DC алдагдал ба үржүүлгийн шинж чанартай хувьсах гүйдлийн алдагдал.

Тогтмол гүйдлийн алдагдал нь ADC дээрх хүчдэлийн дохио 0V орчим биш харин VDD/2 орчим хэлбэлздэгтэй холбоотой юм. VDD/2 тогтмол гүйдлийн түвшин нь ойролцоогоор 64 -ийн дижитал DC уншилттай тохирч байх ёстой ([1] -д заасан дельта).

DC спектрийн алдагдлыг засах алхамууд:

1) Дугтуйны коэффициентийг одоогийн давтамжаар тооцоолно уу.

2) GI (бодит) ба GQ (төсөөлөлтэй) гэсэн хоёр олдог хүчин зүйлийг тооцоол.

3) Бодит регистрийн утгаас дельта * GI, төсөөллийн регистрийн утгаас дельта * GQ хасна.

Ашигласан материал:

[1] Леонид Мациев, "Системийн гүйцэтгэл, олон талт байдлыг сайжруулах

AD5933 , Electronics 2015, 4, 1-34 гэх мэт нэг давтамжтай DFT илрүүлэгчид; doi: 10.3390/electronics4010001

[2] Konrad Chabowski, Tomasz Piasecki, Andrzej Dzierka, Karol Nitsch, "AD5933 нэгдсэн хэлхээнд суурилсан энгийн өргөн давтамжийн эсэргүүцлийн тоолуур", Метрол. Хэмжих. Сист., Боть. XXII (2015), No1, хуудас 13-24.

Алхам 7: Нарийвчилсан зүйл: Спектрийн алдагдал (AC)

Тогтмол гүйдэл алдагдахтай адил АС -ийн алдагдлыг математик аргаар засч залруулж болно. [1] -д эсэргүүцэл ба урвалыг тус тусад нь A*cos (phi) ба A*sin (phi) гэж нэрлэдэг бөгөөд А нь эсэргүүцлийн хэмжээтэй, phi нь фазын өнцөгтэй (PA) харгалзана.

АС спектрийн алдагдлыг засах алхамууд:

1) Дугтуйны коэффициентийг (DC-тэй адил биш) одоогийн давтамжийг тооцоолно уу.

2) a, b, d гэсэн гурван хүчин зүйлийг тооцоол. (өндөр давтамжийн ойролцоо утга: a = d = 256 ба b = 0)

3) Эсэргүүцэл (Acos (phi)) ба урвалын (Asin (phi)) тоон нэгжээр тооцоолох боломжтой боллоо.

Ашигласан материал: [1] Леонид Мациев, "AD5933 гэх мэт нэг давтамжтай DFT илрүүлэгч дээр суурилсан системийн гүйцэтгэл, олон талт байдлыг сайжруулах", Электроникс 2015, 4, 1-34; doi: 10.3390/электроник 4010001

[2] Konrad Chabowski, Tomasz Piasecki, Andrzej Dzierka, Karol Nitsch, "AD5933 нэгдсэн хэлхээнд суурилсан энгийн өргөн давтамжийн эсэргүүцлийн тоолуур", Метрол. Хэмжих. Сист., Боть. XXII (2015), No1, хуудас 13-24.

Алхам 8: Дэвшилтэт зүйл: онолын ашиг-хүчин зүйл

DFT -ийн математик загварчлалыг харгалзан AFE -ийг бүхэлд нь математикаар загварчлах боломжтой байх ёстой. Математикийн хувьд хүчдэлийн дохиог өгөгдсөн тогтмол давтамжтай синус функц, тогтмол гүйдлийн офсет ба оргил далайцтай хувьсах гүйдлийн хэлбэлзэлээр дүрсэлж болно. Давтамжийн алхам хийх явцад давтамж өөрчлөгддөггүй. Ашиг орлого-хүчин зүйл нь зөвхөн эсэргүүцлийн хэмжээг өөрчилдөг болохоос ТХГН-ийн хувьд бид энд дохио өдөөгдсөн фазын шилжилтийг анхаарч үзэхгүй.

AFE -ээр дамжих хүчдэлийн дохионы товч тоймыг энд оруулав.

1) Дахин хэвийсэн үе шат дууссаны дараа АС-ийн далайц Upeak = 1.5V (1V @ VDD = 3.3V) хэвээр байх бөгөөд DC офсет нь VDD/2 болж өөрчлөгдсөн байна.

2) Одоогийн мэдрэгч резистор дахь хүчдэл нь өмнөх үе шаттай адил хэвээр байна …

3) … гэхдээ op-amp-ийн хөрөөдөх хүчдэлийн улмаас хувьсах гүйдлийн хэлбэлзэл нь Z*Upeak/Rcurrent хэмжээтэй байна. (Тогтмол гүйдлийн алдагдлыг VDD/2 - хөрөөний хөрөө эргэх цэгийн хүчдэлийн хүчдэлээр цуцалж, хэлхээний энэ хэсэгт хүчирхэг газар болно)

4) Амп-ийн нэгдэл нь VDD/2-ийн DC офсетыг буцааж оруулаад AD5933-ийн оролтын шатанд дохио дамжуулдаг.

5) Оролтын үе дэх op-amp нь A = -RFB/Rin-ийн өсөлттэй бөгөөд AC далайц нь (Z*Upeak/Rcurrent)*(RFB/Rin) болно.

6) ADC -ийн өмнөхөн 1 эсвэл 5 гэсэн хоёр тохируулгатай програмчлагдах өсгөгч (PGA) байдаг тул ADC дээрх хүчдэлийн дохио нь: PGA*(Z*Upeak/Rcurrent)*(RFB/Rin) болно.

ADC нь 12 битийн нарийвчлалтайгаар v (t) дохиог x (t) = u (t) / VDD * 2^7 дижитал дохио болгон хөрвүүлдэг.

A хэмжигдэхүүн нь Z эсэргүүцэлтэй Z -тэй тэнцүү бөгөөд A = k * Z гэсэн утгатай бөгөөд ойролцоогоор k = PGA * Upeak * RFB * 2^7 / (VDD * Rcurrent * Rin) утгатай байна.

Хэрэв та g-1 / k ба Z = g * A-ийн оронд ашиг олох хүчин зүйлтэй ажиллах дуртай бол.

Алхам 9: Нарийвчилсан зүйл: ТХГН -ийн Shift

[2] -д тэд ТХГН -ийн системчилсэн өөрчлөлтийг давтамжийн функц гэж үздэг. Энэ нь өдөөх дохио үүсгэдэг DAC болон ирж буй дохиог гарах дохиогоор эргүүлэх шаардлагатай DFT хоорондох хугацаа хоцорч байгаатай холбоотой юм.

Шилжилт нь цаг мөчлөгийн тоогоор тодорхойлогддог бөгөөд AD5933 дээр DAC ба DFT хоорондох дохио хоцорч байна.

Ашигласан материал: [1] Леонид Мациев, "AD5933 гэх мэт нэг давтамжтай DFT илрүүлэгч дээр суурилсан системийн гүйцэтгэл, олон талт байдлыг сайжруулах", Электроникс 2015, 4, 1-34; doi: 10.3390/электроник 4010001

[2] Konrad Chabowski, Tomasz Piasecki, Andrzej Dzierka, Karol Nitsch, "AD5933 нэгдсэн хэлхээнд суурилсан энгийн өргөн давтамжийн эсэргүүцлийн тоолуур", Метрол. Хэмжилт. Сист., Боть. XXII (2015), No1, хуудас 13-24.

Зөвлөмж болгож буй:

Эсэргүүцлийн эсэргүүцлийг хэрхэн хэмжих вэ: 7 алхам

Эсэргүүцлийн эсэргүүцлийг хэрхэн хэмжих вэ: Эсэргүүцлийн эсэргүүцлийг хэмжихдээ ихэвчлэн хоёр аргыг ашигладаг. Хэрэглэсэн эхний арга бол резисторын өнгөний код юм. Энэ арга нь тодорхой нарийвчлалтайгаар тоног төхөөрөмжгүйгээр үнэ цэнийг олох аргыг санал болгодог. Хоёрдахь арга бол олон

Өөрийн эсэргүүцлийн шалгагчийг хий: 4 алхам

Өөрийн эсэргүүцэл шалгагчийг хий: Танд хэрэгтэй зүйл: Хуучин Twist төрлийн EGO батерей Хамгийн хямд мультиметрийг олж болно. (Та үүнийг Harbor Freight дээрээс 6.99 доллараар авах боломжтой. Би долоо хоног тутмын зар сурталчилгаадаа купоноор үнэгүй авч өгсөн.) Гагнуурын хэрэгсэл (би амьдралдаа ердөө 2-3 удаа гагнасан. Би

Энгийн сөрөг эсэргүүцлийн өсгөгч LED: 4 алхам

Энгийн сөрөг эсэргүүцлийн өсгөгч LED: Бүгдэд нь энэ өдрийн мэнд! Сөрөг эсэргүүцлийн идэвхгүй бүрэлдэхүүн хэсгүүдийн талаар өнөөдөр бага зэрэг яригдаж байна.Учир нь тэдгээрийг ихэвчлэн эрт дээр үед радар илрүүлэгч технологийг ашиглан анх удаа ашигладаг байсан тул "Туннель диод"; Энэ өдөр сонирхолтой санагдлаа

Жижиг алхамтай ачааллын эсэргүүцлийн банк: 5 алхам

Жижиг алхамтай ачааны эсэргүүцлийн банк: Ачааллын эсэргүүцэл бүхий банкууд нь цахилгаан бүтээгдэхүүнийг турших, нарны хавтангийн шинж чанарыг тодорхойлох, туршилтын лаборатори болон үйлдвэрүүдэд шаардлагатай байдаг. Реостатууд нь ачааллын эсэргүүцлийг тасралтгүй өөрчлөх боломжийг олгодог. Гэсэн хэдий ч эсэргүүцлийн үнэ цэнэ буурах тусам хүч

Цаасан эсэргүүцлийн тооцоолуур: 8 алхам

Цаасан резистор тооцоолуур: Энд картын цааснаас хийж болох гурван залгах жижиг резистор тооцоолуур байна. Энэ хувилбарт хүлцлийн туузыг оруулаагүй болно, гэхдээ хэрэв хангалттай сонирхол байгаа бол надад шугам үлдээгээрэй, би дизайныг өөрчилж болно