Агуулгын хүснэгт:

- Зохиолч John Day day@howwhatproduce.com.

- Public 2024-01-30 11:00.

- Хамгийн сүүлд өөрчлөгдсөн 2025-01-23 15:00.

JDM бол алдартай PIC програмист юм, учир нь энэ нь цуваа порт, хамгийн бага бүрэлдэхүүн хэсгүүдийг ашигладаг бөгөөд цахилгаан хангамж шаарддаггүй. Гэхдээ сүлжээнд олон програмистын хувилбарууд байдаг бөгөөд эндээс аль PIC -тэй ажилладаг вэ? Энэхүү "зааварчилгаа" -нд бид JDM -ийг туршиж үзсэн бөгөөд би таны бүх асуултанд хариулах Spice ашиглан хэлхээг хэрхэн дуурайхыг харууллаа!

Хангамж

LTspice -ийг аналог төхөөрөмжөөс татаж авах боломжтой энд.

Энд танд JDM хэлхээний файлууд хэрэгтэй болно.

Алхам 1: Цуваа портын шаардлага

JDM нь EIA232-ийн тодорхойлолтод нийцсэн цуваа порт шаарддаг бөгөөд хамгийн тохиромжтой нь +12/-12 хүчдэлийн түвшин юм.

Texas Instruments Line Driver MC1488 мэдээллийн хуудасны дагуу (Зураг 3)

Гаралтын эсэргүүцэл = 4V/8mA = 500 ом.

Богино залгааны гүйдлийн хязгаар = 12мВ, хугацааны хязгааргүй - чипт гэмтэл байхгүй.

Шугам хүлээн авагчийн оролтын эсэргүүцэл = 3к -аас 7к ом хүртэл байхыг зөвлөж байна.

Хуучин ширээний компьютер дээрх цуваа портууд энэ шаардлагыг хангасан +12v/-12V ашигладаг.

Шинэ зөөврийн компьютер дээрх цуваа портууд нь бага хүчдэлийг ашигладаг. JDM ажиллахгүй эсвэл ажиллахгүй байж магадгүй - хариулт нь илүү төвөгтэй юм.

Алхам 2: PIC програмчлалын шаардлага

PIC програмчлалын шаардлагын талаархи мэдээллийг Microchip -ээс авдаг. Дээрх нь ердийн төхөөрөмжид зориулагдсан болно.

Алхам 3: JDM -ийн тодорхойлолт

JDM -ийн анхны вэбсайт богино хугацаанд алга болсон уу? Энэ нь дизайнер анх техникийн тодорхойлолтод зориулагдсан зүйлийг таах боломжийг бидэнд олгодог.

- VDD = 5V, хамгийн ихдээ IDD = 2mA хүртэл өгөх ("залгуурт" хувилбарт)

- VHH = 13V, хамгийн ихдээ IHH = 0.2mA хүртэл хангах.

- MCLR Rise time tVHHR = 1uS max.

- ICSP хувилбар нь MCLR-ийг зорилтот түвшний 22к таталтын эсрэг бага татах чадвартай байх ёстой.

Алхам 4: Хэлхээний тодорхойлолт

Зураг JDM1 нь PICPgm вэбсайтаас авсан "стандарт" JDM хэлхээнд үндэслэсэн болно. Энэ бол "PIC in Socket" програмист бөгөөд PIC нь TX болон RTS тээглүүрээс тэжээл авдаг. Анхны диаграмыг ойлгоход хэцүү байсан тул би үүнийг дээрээс доош гүйдлийн урсгалын ердийн дүрмийг ашиглан дахин зурсан болно. Мөн би барилгын болон туршилтын явцад шаардлагатай "RESET", "PROG", "RTS" LED үзүүлэлтүүдийг нэмсэн. Эдгээр нь зан төлөвт муугаар нөлөөлөхгүй гэж найдаж байна.

Хэлхээний дизайны ердийн уламжлал нь бүх үндэслэлтэй байдаг боловч JDM -ийн гол онцлог нь цуваа портын газардуулга (GND) нь VDD -тэй холбогдсон явдал юм. Цуваа портын дохиог GND, PIC дохиог логик газар (VSS) -тай харьцуулахад хэмждэг тул энэ нь төөрөгдөл үүсгэдэг.

TX өндөр байх үед Q1 нь урагш чиглэсэн хоёр диод шиг ажилладаг. (Q1 цуглуулагч нь транзисторын хэвийн ажиллагаатай адил урвуу байрлалтай байдаггүй). Q1 коллектор нь C2 цэнэглэдэг бөгөөд үүнийг Zener (D3) VDD+8V дээр хавчуулдаг. Q1 ялгаруулагч нь 13V -ийг MCLR -д Програм/Баталгаажуулах горимд хүргэдэг.

TX буурахад C3 конденсаторыг D1-ээр цэнэглэж, VSS-ийг zener (D5) -ээр VDD-5V дээр хавчдаг. Мөн TX-ийг D1-ээр (VSS-0.6) хавчих юм. Q1 унтраалттай, C1 нь дараагийн програмчлалын импульсийн цэнэгээ барьдаг. MCLR нь D2 -ээр 0V -ээр бэхлэгдсэн тул PIC -ийг дахин тохируулах болно.

RTS өндөр байх үед цагийг PGC руу дамжуулдаг. D4 хавчаар PGC нь VDD логик дээр өндөр байна. RTS бага үед C3 конденсаторыг D6-ээр цэнэглэж, VSS-ийг zener (D5) -ээр VDD-5V дээр хавчдаг. D6 нь PGC -ийг VSS эсвэл логик 0 дээр хавчуулдаг.

Програмчлалын явцад DTR дээр илгээсэн өгөгдлийг PGD дээр уншдаг бөгөөд үүнийг PIC оролт болгон тохируулдаг. DTR өндөр байх үед Q2 нь "ялгаруулагч дагагч" үүрэг гүйцэтгэдэг бөгөөд PGD хүчдэл нь ойролцоогоор (VDD-0.6) эсвэл логик 1. DTR бага байвал Q2 нь муу транзисторын үүргийг гүйцэтгэдэг (ялгаруулагч ба коллекторын зүү нь эсрэг чиглэлд). Q2 нь VSS эсвэл логик 0 дээр D7 -ээр бэхлэгдсэн PGD -ийг бага хэмжээгээр татаж авдаг.

Баталгаажуулах явцад PIC нь PGD -ийг цуваа порт руу өгөгдөл илгээх гаралт болгон тохируулдаг. DTR өндөр байх ёстой бөгөөд өгөгдлийг CTS дээр уншдаг. PGD гаралт өндөр байх үед Q2 унтарсан, CTS = DTR = +12V. PGD гаралт бага байх үед Q2 асаалттай байна. Q2 цуглуулагч нь DTR -ээс одоогийн (12V+5V)/(1k+1k5) = 7mA -ийг татаж, CTS -ийг бага хэмжээгээр VSS рүү татдаг.

Алхам 5: Симуляцид бэлтгэ

LT spice татаж аваад энд өгөгдсөн хэлхээний файлуудыг (*.asc) хадгалж нээнэ үү. Хэлхээг дуурайхын тулд бид түүнд хэд хэдэн оролт өгч, дараа нь гаралтыг "мөрдөх" ёстой. V1, V2 V3 нь 12V цуваа портыг R11, R12, R13 гаралтын эсэргүүцэлтэй дуурайдаг.

- V1 нь TX дээр 0.5ms -аас 4.5ms хүртэл 2 програмын импульс үүсгэдэг

- V2 нь DTR дээр 1.5 -аас 4.5 мс хүртэл өгөгдлийн импульс үүсгэдэг

- V3 нь RTS дээр 0.5 -аас 3.5 мс хүртэл цагийн импульс үүсгэдэг

V4, X1, R15, R16 бүрэлдэхүүн хэсгүүд нь симуляцийн нэг хэсэг юм.

- V4 нь өгөгдлийг шалгахын тулд 2.5 -аас 4.5 мс хүртэл 2 импульс үүсгэдэг.

- Jumper X1 нь PGD дээрх OUTPUT -ийг дуурайдаг.

- R15, R16 нь VDD ба MCLR дээр PIC -ийн "ачаалал" -ыг дуурайдаг.

Алхам 6: ICSP -ийн өөрчлөлт

Зураг JDM3 нь "хэлхээний" програмчлалын хувилбарыг харуулж байна. Оригинал хувилбараас гарсан өөрчлөлтүүд байна

- ZIF залгуурыг ICSP холбогчоор солих.

- PIC одоо зорилтот хэлхээний хангамжаар тэжээгддэг (V5).

- 5V zener (D5) -ийг салга.

- Бяцхан 100pF конденсаторыг (C4) зорилтот хэлхээний PIC -ийн хажууд зөөв.

- LED нь боломжтой бол хэлхээний самбараас тэжээл авдаг.

- Зорилтот хэлхээнд MCLR татах эсэргүүцэл (R10) ба диод (D10) шаардлагатай.

- АНХААРУУЛГА. Зорилтот самбар нь "хөвөгч" хангамжтай байх ёстой, хамгийн тохиромжтой нь батерей юм.

- Зорилтот газар (VSS) -ийг бусад компьютерын портуудыг JDM -тэй нэгэн зэрэг холбосноор компьютер/PC -ийн газартай бүү холбоорой.

JDM1 -ийг дуурайсны дараа С2 дээр удаан цэнэглэх асуудал гарч ирэв. Дараа нь Fruttenboel -ийг уншсаны дараа C2 ба Q1 -ийг анхны хувилбар болгон оруулсан болно. Асуудал үүсгэхээс гадна С2 ба Q1 юу хийх гэж байгааг би бодож чадахгүй байна. Тиймээс JDM4 -ийн хувьд бид Fruttenboel дээрх хуучин загвар руу буцаж очсон бөгөөд үүнийг ойлгоход хялбар юм. VSS ба VDD+8V хооронд D1 ба D3/LED2 хавчаар MCLR. R1 -ийн утга нь 3к3 болж буурсан бөгөөд энэ нь LED2 -ийг 12V -т гэрэлтүүлэхэд хангалттай юм.

JDM4 нь сул цуваа портуудтай ажиллахад зориулагдсан болно. TX өндөр байх үед (+9V), TX гүйдлийн эх үүсвэр = (9-8)/(1k +3k3) = 0.2ma, энэ нь LED2-ийг гэрэлтүүлэхэд хангалтгүй боловч MCLR-ийг өндөр татахад л хангалттай. TX буурахад (ойролцоогоор -7V) TX гүйдлийн угаалтуур = (9-7)/1k = 2mA. LED1 гүйдэл = (LED хувьд 7-2)/(2k7) = 1.8mA. MCLR гүйдлийг бууруулна уу = 7-5.5/3k3 = 0.5mA.

Энэ хэлхээг туршсан (JDM5 симуляци) +/- 7V цуваа портууд юу болж байгааг харахын тулд VHH = 13V-ийг хангах хүчдэл хангалтгүй байна. C1 -ийн зорилго одоо тодорхой болж байна, C1 нь MCLR -ийн богино +хүчийг бий болгодог, TX -ийн өсөн нэмэгдэж буй ирмэг дээр 33us нэмэгдэх бөгөөд энэ нь PIC програмчлалын горимд ороход хангалттай урт байх болов уу? Гэхдээ MCLR -ийг бага ба LED1 -ийг хамт гэрэлтүүлэх хангалттай гүйдэл байхгүй тул X2 холбогчийг (LED1 -ийг идэвхгүй болгох) салга. TX буурах үед TX гүйдэл угаалтуур = (7V-5.5V)/(1k+3k3) = 0.3mA, MCLR-ийг татах R10-ийн эсрэг бага татахад л хангалттай.

Алхам 7: Загварчлалын үр дүн

График файлуудыг үзэхийн тулд доорх линкүүд дээр хулганы баруун товчийг дараад "Холбоосыг шинэ таб дээр нээх" -ийг сонгох нь дээр.

Симуляци 1: анхны JDM1 -ийн MCLR, VSS, RTS -ийн ул мөр. 1, 2, 3 -р ажиглалт шууд гарч байна.

Симуляци 2: MCLR ба VSS болон RTS -ийн ул мөр нь өмнөх асуудлуудыг зассан JDM2 -ийг өөрчилсөн болно.

Симуляци 3: програм горимд өгөгдөл илгээх JDM2 -д зориулсан PGD, VSS, PGC -ийн ул мөр. Ажиглалт 4, 3.5mS.

Симуляци 4: шалгах горимд JDM2 -д зориулсан PGD, VSS болон CTS -ийн ул мөр (X1 холбогчийг оруулсан). БОЛЖ БАЙНА УУ

Симуляци 5: MCLR, VSS, PGD ба PGC -ийн ул мөр JDM3 -д зориулагдсан болно. ICSP хэлхээний хүчийг ашиглан олон асуудлыг шийддэг.

Симуляци 6: +/- 9V цуваа порттой JDM4-ийн MCLR, VSS, PGD, PGC-ийн ул мөр. MCLR нэн даруй босч, бүрэн ажиллаж байна.

Симуляци 7: +/- 7V цуваа порт, X2 холбогчтой JDM5-ийн MCLR, VSS, TX-ийн ул мөрийг арилгасан. C1 нь MCLR -ийн өсөн нэмэгдэж буй ирмэг дээр MCLR -ийг TX -ээс 13V хүртэл түлхэхэд хангалттай хэмжээний +өсөлтийг бий болгодог.

Алхам 8: Дүгнэлт

Spice нь хэлхээний ажиллагааны "далд нууц" -ыг ил гаргахдаа үнэхээр сайн. Мэдээжийн хэрэг JDM хэлхээ нь ажилладаг бөгөөд олон PIC чиптэй нийцдэг боловч дараахь ажиглалтууд нь боломжит хязгаарлалт/нийцтэй байдлын асуудал/алдааг илрүүлж байна уу?

- MCLR -ийн урт хугацааны өсөлт, C2 нь TX -ийн эхний импульс дээр VPP -д цэнэглэгддэг. Тодорхойлолт амжилтгүй болсон 3.

- TX өндөр, RTS буурах үед цуваа порт нь C2 цэнэглэгддэг. Гэхдээ RTS нь C3 цэнэглэх үүрэгтэй. Хэрэв хоёулаа нэгэн зэрэг тохиолдвол энэ нь RTS дээр илүү их ачаалал өгдөг бөгөөд ингэснээр симуляц хийх үед C3 цэнэгээ алдаж (VSS нэмэгддэг). Тодорхойлолт амжилтгүй болсон 1.

- Цагны импульс 3.5ms дээр зогссоны дараа C3 цэнэгээ алддаг (VSS өсч эхэлдэг).

- С2 -ийн зорилго нь юу вэ, энэ нь огт хэрэгтэй юу?

Шийдлүүд

- PICPgm нь "ажлын тойрог" програм хангамжийг ашигладаг байх. Энэ нь урт TX импульсийг C2 -д урьдчилан цэнэглэх ёстой бөгөөд дараа нь зөвхөн хоёр дахь TX импульсийн дараа програмчлалын горимд орох уу? Симуляцийн хувьд би C2 -ийн утгыг 1uF болгон бууруулж, 1ms -ийн өсөлтийг өгдөг. Хамгийн тохиромжтой шийдэл биш.

- C2 ба C3 -ийг хуваасан тул тэд бие даан цэнэглэдэг. JDM2, C2 -ийн нэг жижиг өөрчлөлтийг VSS -ийн оронд GND гэж нэрлэдэг.

- JDM3 -аар шийдсэн. PIC нь зорилтот хэлхээгээр тэжээгддэг тул ICSP нь илүү найдвартай байдаг.

- JDM4 нь асуудлыг шийддэг 1. Энэ бол C2 -ийг бүрмөсөн устгах энгийн загвар юм.

Алхам 9: Эцэст нь

Идээний нотолгоо бол идэх явдал юм. Энэ JDM ажилладаг тул үүнийг үргэлжлүүлэн ашиглаарай.

Мөн миний зөвлөмжүүд:

- сокет програмчлал болон 12V цуваа портуудад JDM2 ашиглах,

- ICD програмист болон +/- 9V-ээс дээш цуваа портод JDM4 ашиглах,

- +/- 7V-ээс дээш цуваа портуудад X2 холбогчийг салгасан JDM4-ийг ашиглана уу.

Ашигласан материал:

Аналог төхөөрөмж LT амтлагч

picpgm

Fruttenboel

Зальтай буланд байгаа бусад PIC төслүүдийг дагана уу

Зөвлөмж болгож буй:

Elegoo Super Started Kit Uno R3 тойм: 4 алхам

Elegoo Super Started Kit Uno R3 тойм: Хэдхэн хоногийн өмнө Elegoo надад энэхүү Super Starter Kit -ийг туршихаар илгээсэн. Тиймээс, дотор нь юу байгааг харцгаая. Энэхүү авсаархан хайрцгийг нээхэд бид маш олон зүйлийг харж болно. Нүүрэн дээр бүх бүрэлдэхүүн хэсгүүдийг агуулсан индекс байна. Дотор нь бидэнд бүх зүйлийг агуулсан талархлын хуудас байгаа

KS-Garden: Тойм: 9 алхам

KS-Garden: Тойм: Тойм: KS-Garden-ийг арын хашаанд байгаа цэцэрлэгээ/хүлэмжийн ургамлаа эсвэл дотроо ургадаг хайрцгийн ургамлаа усжуулах/агааржуулах зориулалтаар ашиглаж болно. (Модульчлагдсан загвар) KS-Garden систем нь үндсэндээ дараах модулиудаас бүрдэнэ. системийн хайрцаг - Relais ба цахилгаан хангамжийн хайрцаг

Ардуино ISP байдлаар -- AVR дээр Hex файлыг шарах -- AVR дахь гал хамгаалагч -- Ардуино програмистын хувьд: 10 алхам

Ардуино ISP байдлаар || AVR дээр Hex файлыг шарах || AVR дахь гал хамгаалагч || Ардуино програмистын хувьд: ……………… Миний YouTube сувгийг SUBSCRIBE дарж илүү олон видео үзээрэй …….. Энэ нийтлэл Энэ бол isp шиг arduino -ийн тухай юм. Хэрэв та Hex файлыг байршуулахыг хүсч байгаа эсвэл гал хамгаалагчаа AVR дээр тохируулахыг хүсч байвал програмист худалдаж авах шаардлагагүй болно

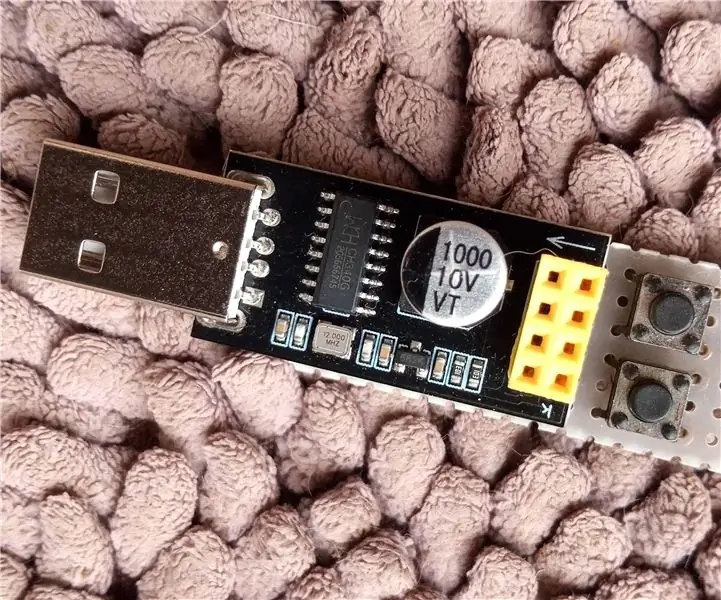

ESP -01 програмистын хакердах нь хялбар: :) 6 алхам

ESP-01 програмист хакердах-хялбар нэг :): Сайн байна уу ESPers, энэ заавар дээр би танд ESP-01 / ESP8266-01 / ES-01 модульд програмист хийх энгийн хакерыг үзүүлэх болно. Бидний ихэнх нь Arduino самбар эсвэл FTDI USB-TTL төхөөрөмжийг энэ модульд програмист болгон ашигладаг байсан. Хоёр арга хоёулаа сайн ажилладаг. Гэхдээ т

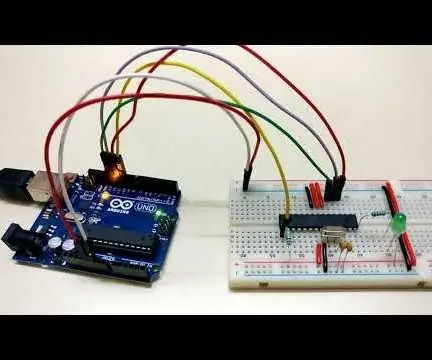

Arduino төслүүдээ хумих - Arduino UNO нь ATmega328P програмистын хувьд (https://youtu.be/YO61YCaC9DY): 4 алхам

Arduino төслүүдээ хумих | ATmega328P програмистын хувьд Arduino UNO (https://youtu.be/YO61YCaC9DY): Видео холбоос: https://youtu.be/YO61YCaC9DYProgramming ATmega328P нь Arduino-ийг ISP (систем доторх програмист) болгон ашиглах нь Arduino-ийн талбар эсвэл функцийг ашиглах боломжийг олгодог. ПХБ. Энэ нь коллежийн төслөө хийхдээ ихэвчлэн тусалдаг. Энэ нь багасгасан